# A Second Life for Flash With Page Isolation

M. Ceylan Morgul, Ph.D. and Mircea Stan, Ph.D. University of Virginia, USA

**Problem**

# Flash Memory – we still depend on it

- Sustainability and Reliability

- Endurance limitation: wear-out by using (Program/Erase cycling)

- System-level and Device-level mitigation techniques

- over-provisioning, wear-leveling, read-retry, etc. Active or Passive Recovery

- Can "bad" blocks be reused?

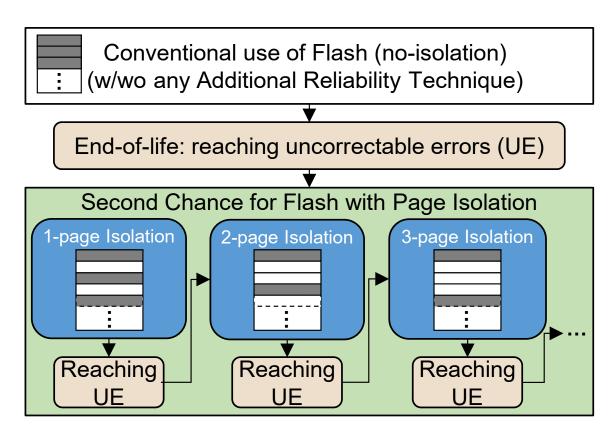

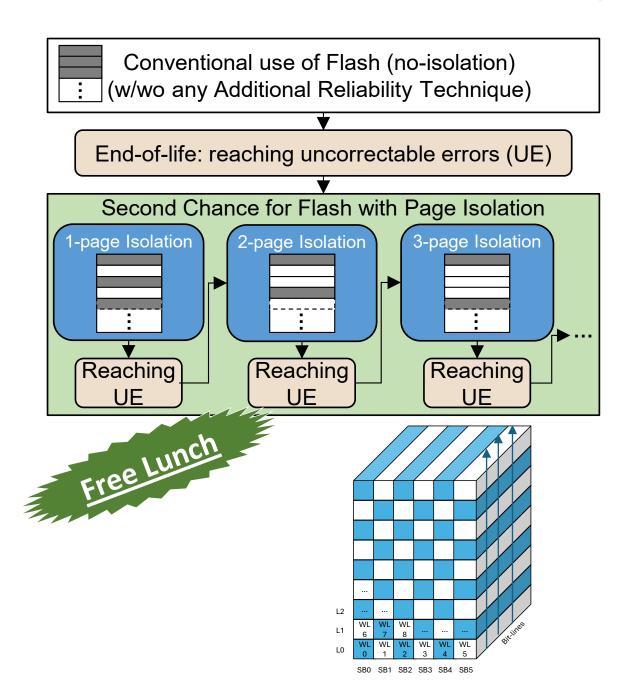

Page Isolation: enables the use of pages after life

#### **Outline**

- We like Flash Memory

- [Device] Reliability of Flash

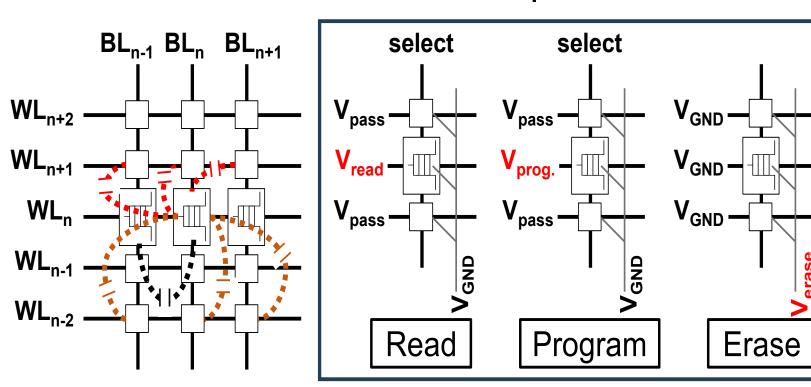

- [Circuit] Program Interference

- Page Isolation

- Experimental Results

- [System] SSD FTL Implementation

- Conclusion

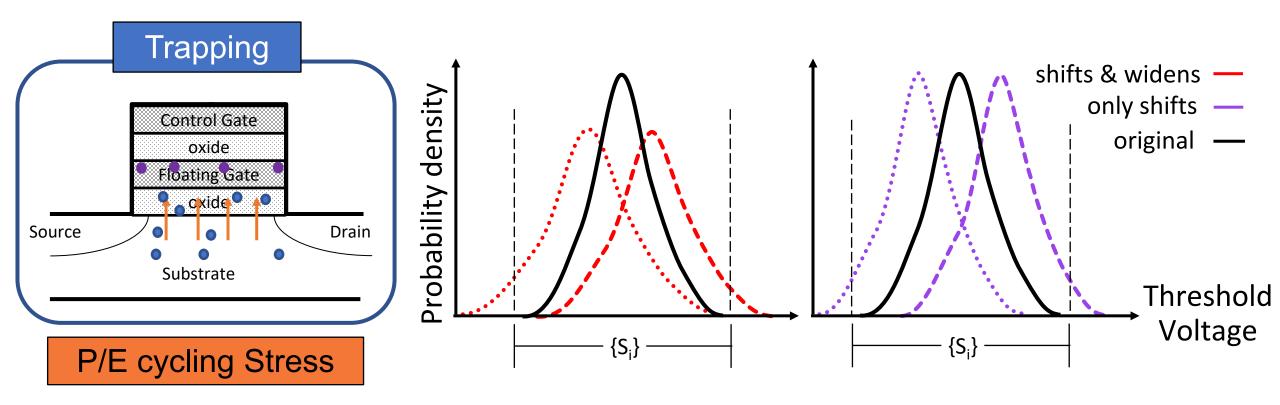

## Reliability of Flash

- Electrons are forcibly moved during Program and Erase operations

- Stress shifts and widens or only shifts threshold voltage pdf

- Cells are not independent

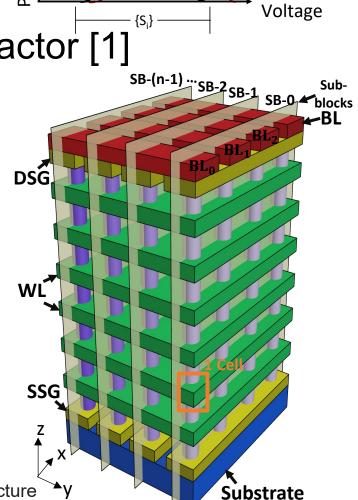

- Cell-to-cell interference is reported as dominant factor [1]

**Threshold**

Probability

[1] Park, Ki-Tae, et al. "A zeroing cell-to-cell interference page architecture with temporary LSB storing and parallel MSB program scheme for MLC NAND flash memories." *IEEE JSSC 2008*

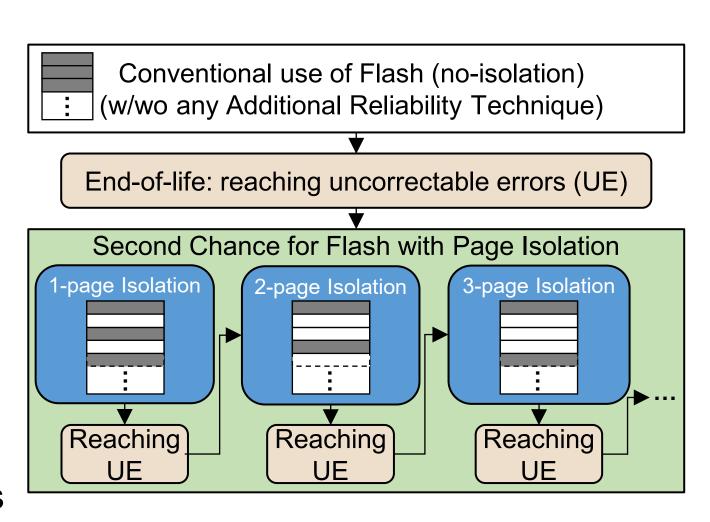

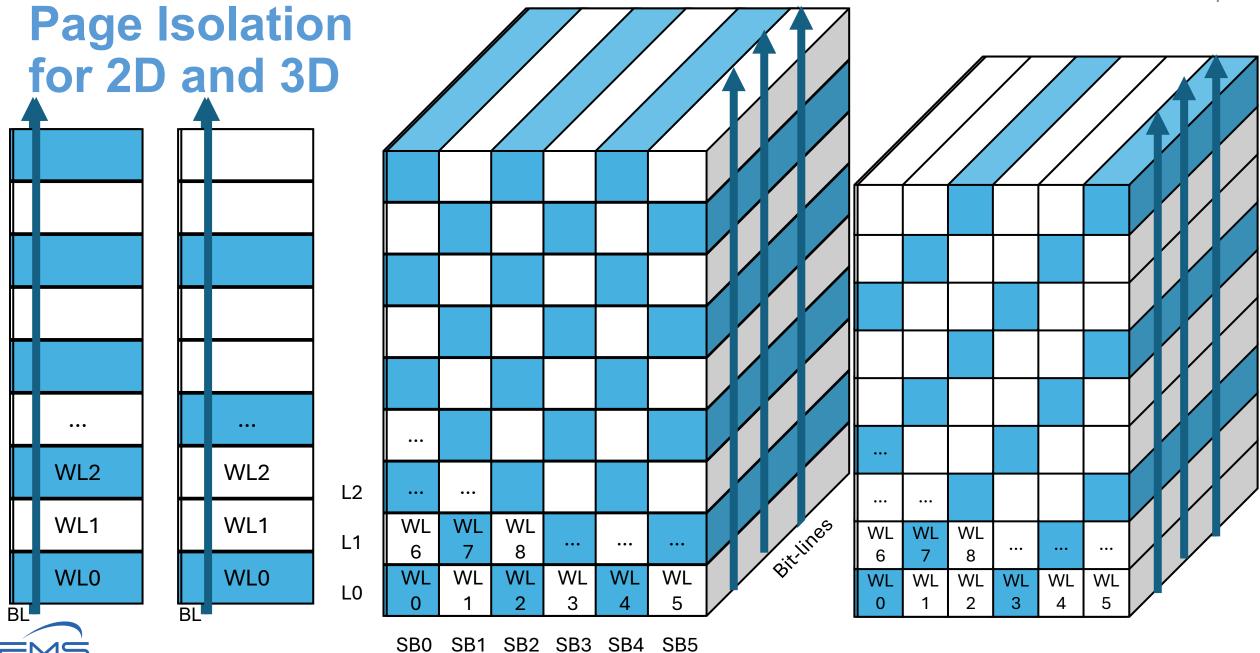

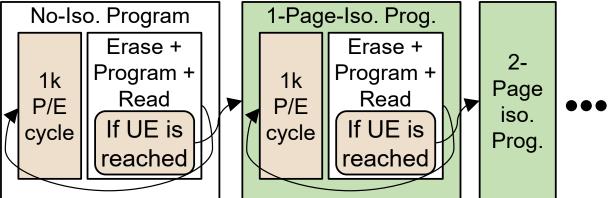

#### Page Isolation

#### <u>ldea:</u>

- Using some pages for isolation to mititgate page interference (and read disturb)

- Enables usage of blocks (pages) otherwise declared as «bad»

- Calibrate read current for low\_level-to-high\_level errors

the Future of Memory and Storage

2-

Page

iso.

Prog.

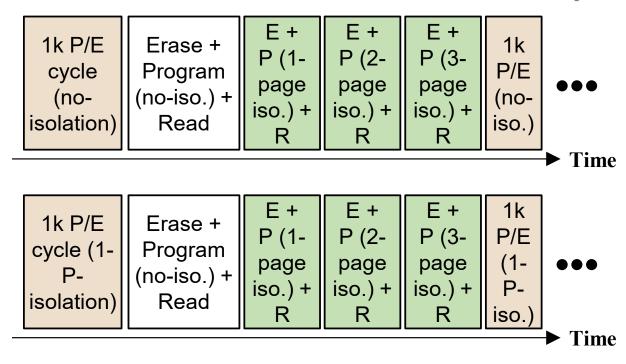

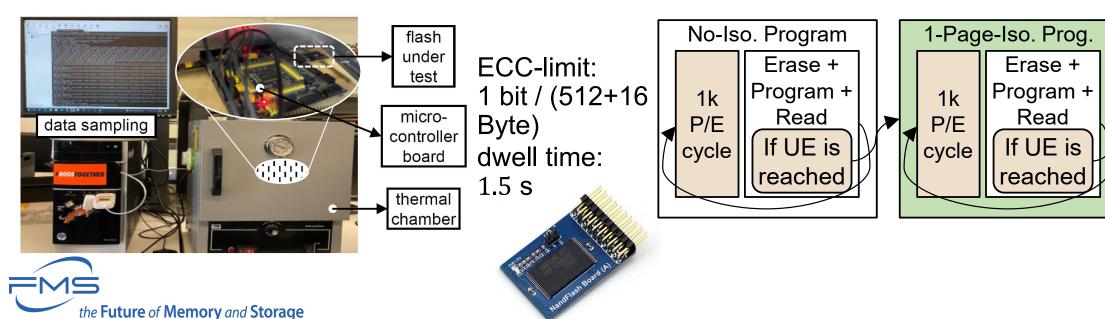

## **Experimental Setup**

- 2D SLC NAND floating gate

- 3D TLC NAND charge trap

- no-ECC and no read-retry

- Data-0 and Random Data

- Tested at different temperatures

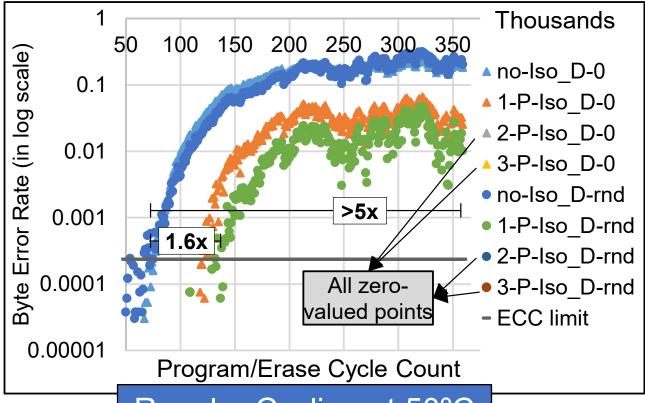

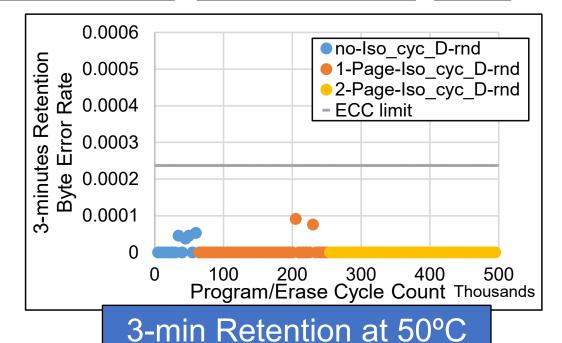

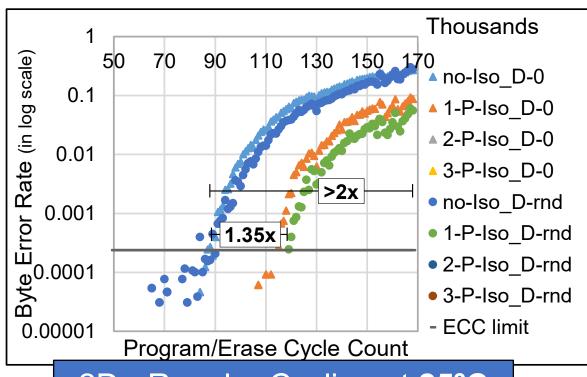

## Page Isolation Enhances Reliability – 2D

- Page isolation reduces the error rate

- Presents additional the lifetime

Regular Cycling at 50°C

1-Page-Iso Cyc. at 50°C

the Future of Memory and Storage

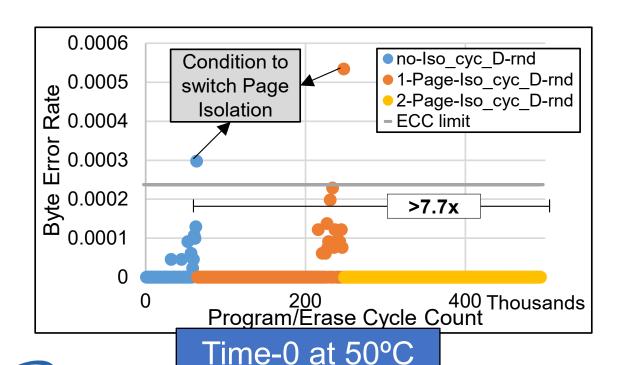

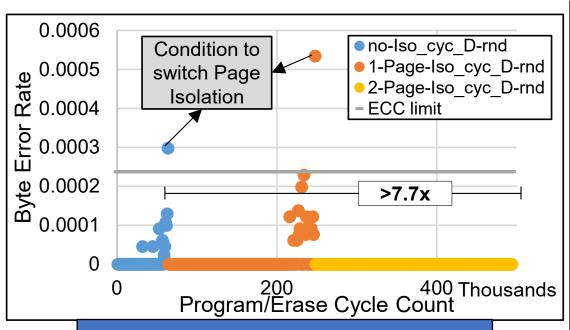

#### **Life After Death with Page Isolation – 2D**

- 50% of pages gets 3.5x extra life

- 33% of gets more than 7.7x

the Future of Memory and Storage

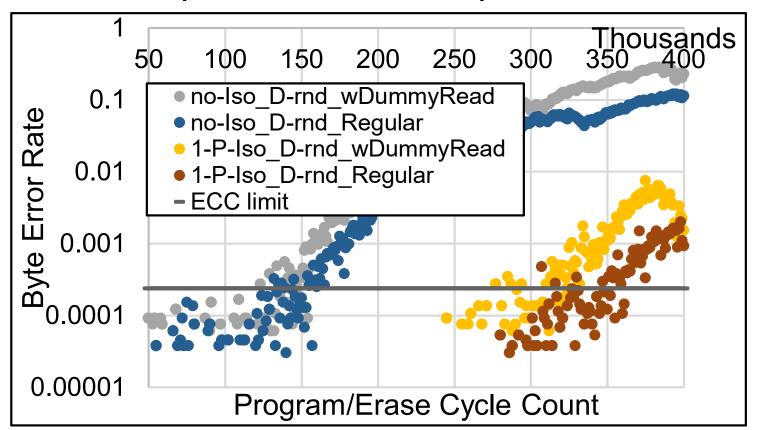

# Read Disturb vs Program Interference – 2D

- 2.4x lifetime improvement with Read Disturb mitigation

- 2.3x lifetime improvement with equalized Read Disturb

1-Page-Iso Cycling at 50°C

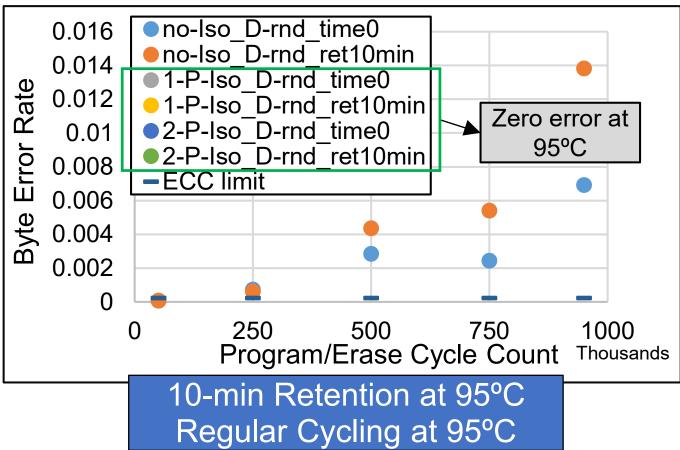

## **Retention and High Temperature – 2D**

Low (zero) error rate even at high temperature retention error

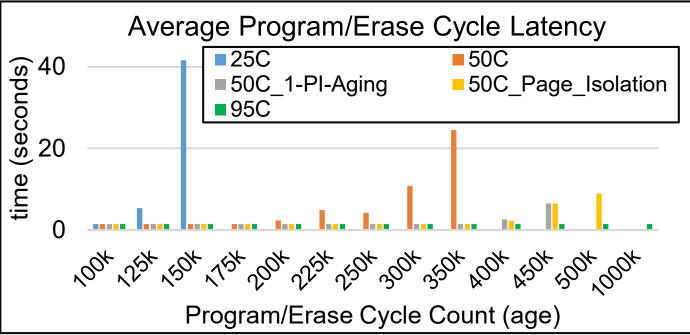

# It still ages: Cycling Latency – 2D

7.7x translates to 6.6x lifetime improvement for performance demanding applications

Page Isolation at 50°C

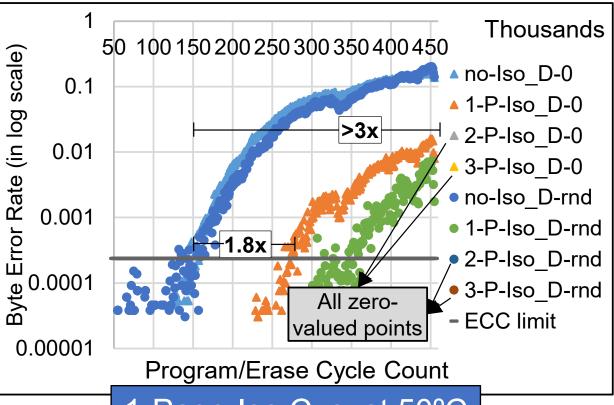

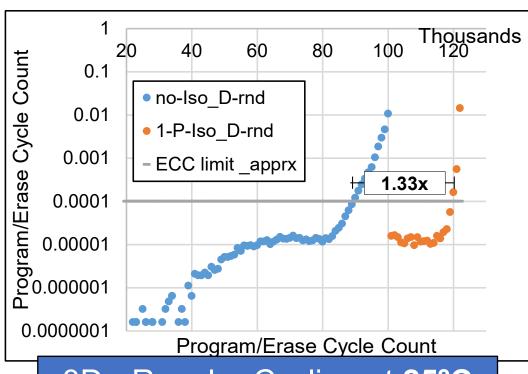

# Life After Death with Page Isolation – 3D vs 2D (wip)

3D benefits Page Isolation less than 2D because of higher dependency – Increasing number of isolation page is needed

3D - Regular Cycling at 25°C

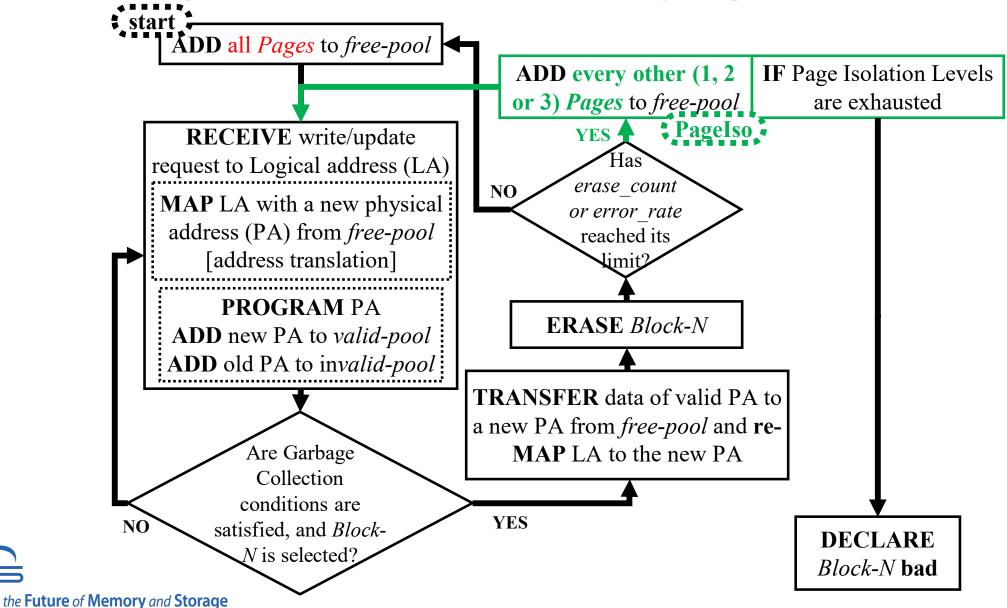

# SSD FTL (Flash Translation Layer) Implementation

#### Conclusion

- Page Isolation:

- For already aged blocks

- At 50°C, 3.5x lifetime for half of the capacity

- >6x lifetime for 1/3 of the capacity

- At 25°C -> 1.3x

- Easy to implement in SSD FTL

- Reduces the capacity loss, which happens due to reliability (and the waste)

#### **Acknowledment**

- I would like to thank my Ph.D. advisor Mircea Stan, University of Virginia.

- I would like to thank Matchima Buddhanoy and her advisor Biswajit Ray, Colorado State University, USA, for 3D NAND Flash Experiments.

- This work was supported in part by Semiconductor Research Corporation (SRC) under the Center for Research on Intelligent Storage and Processing in-memory (CRISP).

- Original Paper is published in IIRW 2024