# High Bandwidth Memory

# Market and Technology Trends

### Presenter:

Simone Bertolazzi, Ph.D.

Principal Analyst at Yole Group

simone.bertolazzi@yolegroup.com

## HIGH BANDWIDTH MEMORY – MARKET & TECHNOLOGY TRENDS

# **Presentation Outline**

Memory Market Dynamics

Overview by Technologies

High-Bandwidth Memory

Ecosystem and Technology Trends

# MEMORY MARKET OVERVIEW

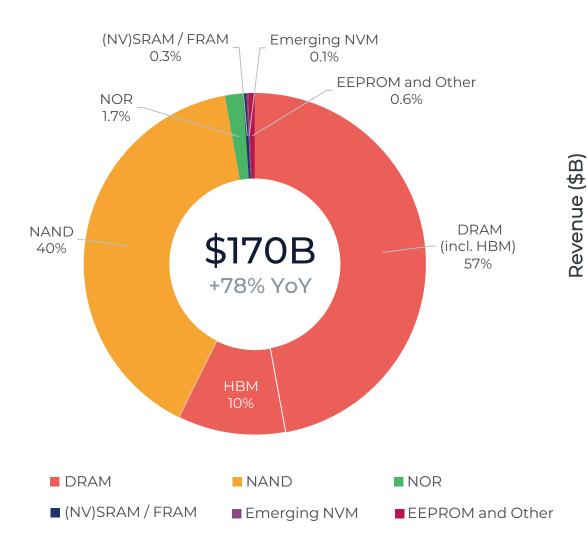

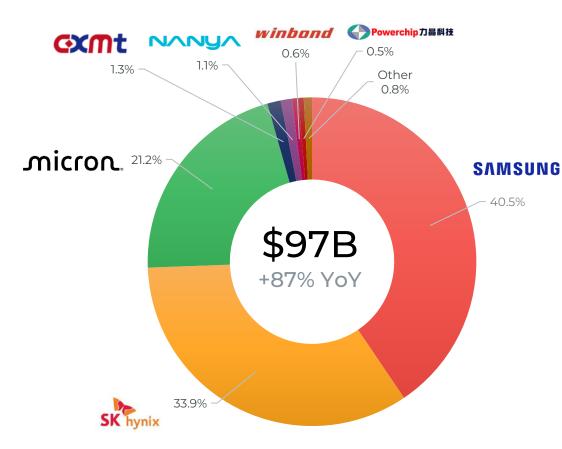

### 2024 Memory Market – Breakdown by Technology

### Memory Market Evolution (2020 – 2025)

Source: "Status of the Memory Industry 2025" by Yole Group

# DRAM MARKET OVERVIEW

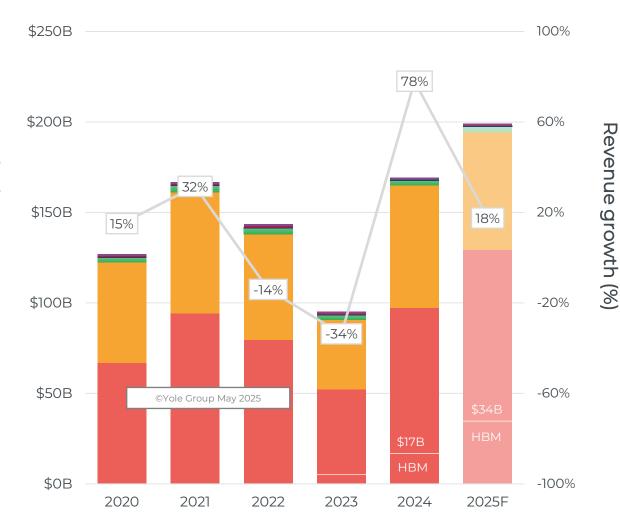

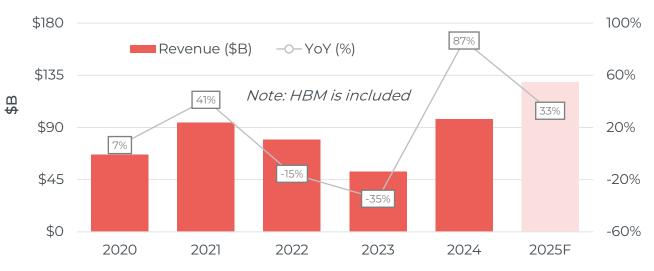

#### 2024 DRAM Market Shares

**Note**: revenues include chips and wafers, as well as memory modules and HBM stacks sold by <u>IDM memory companies</u>.

#### **DRAM Revenue**

### **DRAM Average Selling Price**

\$/Gb

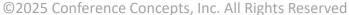

# HBM MARKET OUTLOOK - OVERVIEW

### Revenue (\$B)

HBM revenue (\$B)

CAGR<sub>24-30</sub> ~33%

---- HBM share of DRAM market (%)

### Bit shipments (B GB)

HBM bit shipments (B GB)

CAGR<sub>24-30</sub> ~31%

---- HBM share of DRAM market (%)

### Wafer Production (K WPM)

HBM wafer production (KWPM)

CAGR<sub>24-30</sub> ~18%

---- HBM share of DRAM market (%)

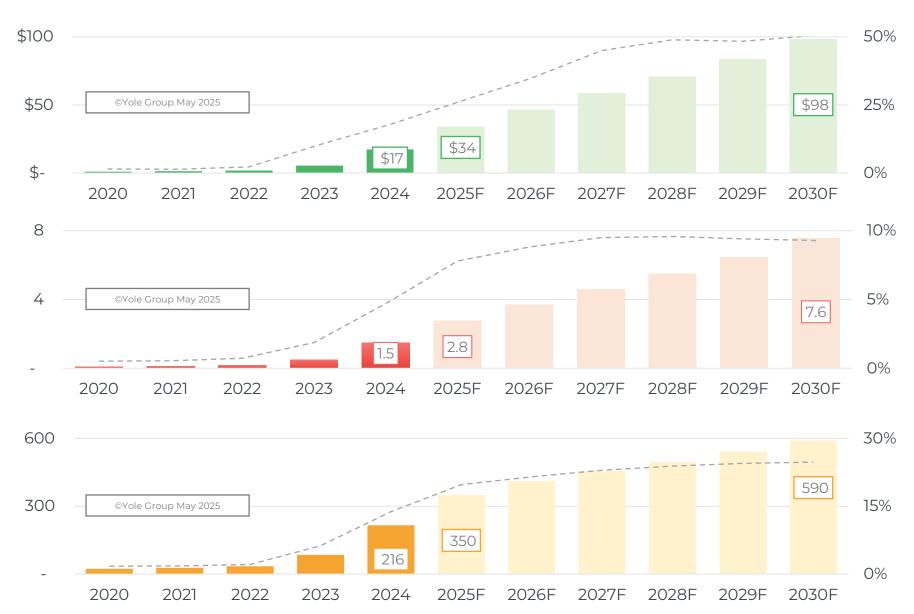

# DRAM BIT DEMAND - FOCUS ON DATA CENTERS

### Al applications are fueling DRAM growth in data centers

• The rise of generative AI – initiated by the release of ChatGPT in November 2022 – and the continuous expansion of data-intensive AI/HPC applications in data centers led to a significant surge in DRAM shipments in 2023. These trends will induce continuous market growth throughout the next five years.

# APPROACHES TO OVERCOME THE MEMORY WALL - OVERVIEW

### HBM, Chiplets, Near- or In-Memory Computing

Low latency is the most important feature. Mainly for applications requiring high bandwidth.

Data is more important for the application.

Mainly for dataintensive

applications.

### Memory moves towards computing

Computing moves towards memory or storage

**DRAM-based** processing in memory

**SAMSUNG**

Samsung AXDIMM solution

### Computational storage

storage drive solution

# Computing

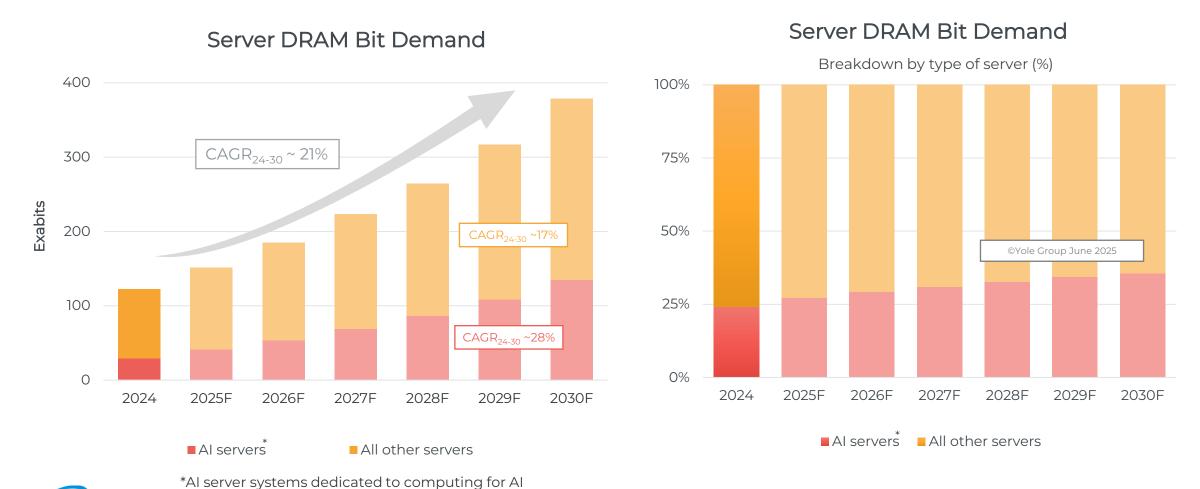

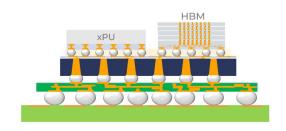

# HIGH-BANDWIDTH MEMORY (HBM)

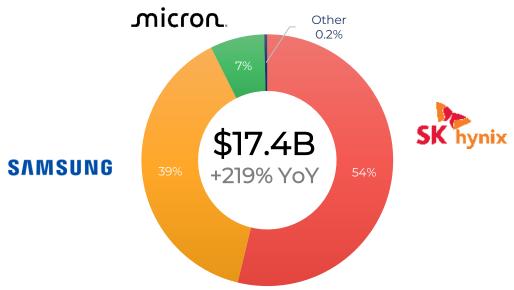

### 2024 HBM Revenue Market Share

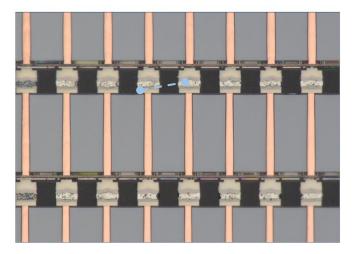

HBM Stack TSV & Microbumps

Source: "SK hynix HBM3" report by Yole Group, 2025

# HIGH-BANDWIDTH MEMORY (HBM)

# Product Development Overview

| HBM generation                                             | НВМ                       | НВМ2                                         | НВМ2Е                                    | НВМ3                         | НВМ3Е                                              | НВМ4                           |

|------------------------------------------------------------|---------------------------|----------------------------------------------|------------------------------------------|------------------------------|----------------------------------------------------|--------------------------------|

| Players with products in the market                        | SK hynix                  | SAMSUNG Flarebolt Aquabolt Aquabolt-XL (PIM) | SAMSUNG<br>Flashbolt SK hynix<br>Micron. | SAMSUNG<br>Icebolt           | SAMSUNG<br>Shinebolt Sk hynix                      | SAMSUNG SK hynix _micron.      |

| Year of first product release                              | 2014                      | 2018                                         | 2020                                     | 2022 - 2023                  | 2024                                               | 2026(E)                        |

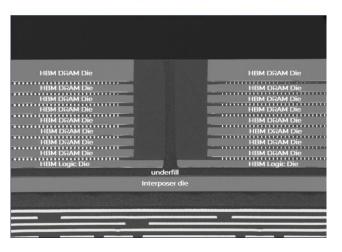

| Typical number of dies per stack (Main packaging approach) | 4Hi<br>(TSV & microbumps) | 4-8Hi<br>(TSV & microbumps)                  | 4-8Hi<br>(TSV & microbumps)              | 8-12Hi<br>(TSV & microbumps) | 8-12Hi (16Hi) <sup>NEW</sup><br>(TSV & microbumps) | 12-16Hi<br>(TSV & microbumps)  |

| Max capacity per stack                                     | 1GB                       | 4-8GB                                        | 8-16GB                                   | 16-24GB                      | 24-36GB (48GB) <sup>NEW</sup>                      | 36-48GB                        |

| Die density<br>(Typical process)                           | 2Gb<br>(2x)               | 8-16Gb<br>(2y, 2z)                           | 16Gb<br>(1y, 1z)                         | 16Gb<br>(1z)                 | 24Gb<br>(1a, 1b/1β)                                | 24Gb (32Gb)*<br>(1b/1β, 1c/1γ) |

| Max data rate                                              | 1Gbps                     | 2-2.4Gbps                                    | 3.2-3.6Gbps                              | 5.6-6.4Gbps                  | 8.0-9.8Gbps                                        | ≥ 6.4Gbps                      |

| Effective bus width                                        | 1,024                     | 1,024                                        | 1,024                                    | 1,024                        | 1,024                                              | 2,048                          |

| Max bandwidth per stack                                    | 128GB/s                   | 205-307GB/s                                  | 460GB/s                                  | 819GB/s                      | 1.2TB/s                                            | ≥ 2TB/s                        |

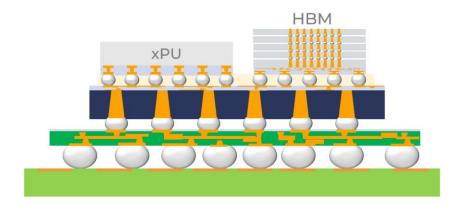

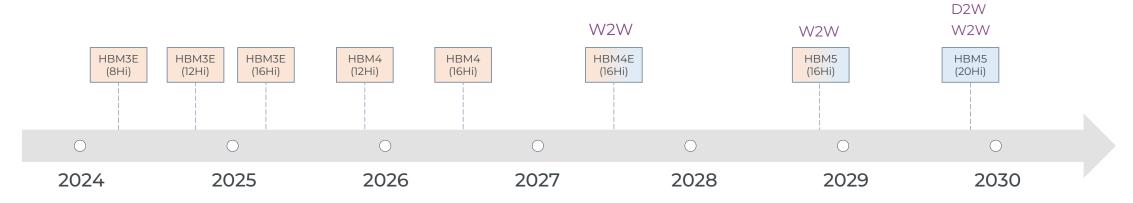

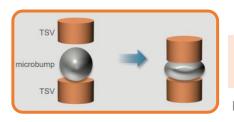

# BONDING TECHNOLOGIES FOR HIGH-BANDWIDTH MEMORY

- Reportedly, wafer-to-wafer (W2W) hybrid bonding will be first used to stack the first DRAM layer and the base/logic layer. The first technologies using this approach will likely be HBM4E/HBM5 (≥16Hi), particularly in customized HBM solutions.

- Collective Die-to-Wafer (D2W) and Die-to-Die (D2D) bonding schemes will be used in subsequent generations. We currently model die-bonding approaches to start from the HBM5 generation from 20Hi.

Mass Production Time For Market Leaders

Technologies based on MR-MUF\* or NCF-TCB\*\* with TSV and microbumps

Image credit: Applied Materials

Technologies that are likely to make use of hybrid (or fusion) bonding

\*MR-MUF: Mass Reflow Molded Underfill

\*\*NCF-TCB: Non-Conductive Film Thermo-Compression Bonding

Source: "Next-Generation DRAM 2025" by Yole Group

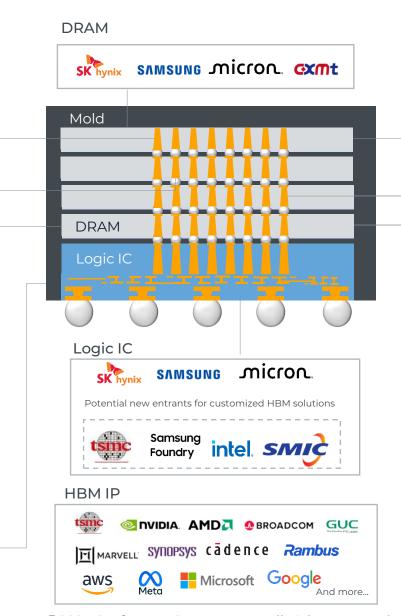

## HIGH-BANDWIDTH MEMORY - DETAILED SUPPLY CHAIN

#### Plating Solution

#### Gases

#### CMP Slurries and Pads

#### Tape (Dicing/Grinding)

Source: "Next-Generation DRAM 2025" by Yole Group

**TSV Process**

TCB Process

(A) Hanwha

APPLIED MATERIALS.

APPLIED MATERIALS

HWATSING

**Molding Process**

ASMPT TOWA

Kulicke & Soffa

**Lam**<sup>®</sup>

**ASMPT**

set

DISCO

YAMADA

Hybrid Bonding (currently in R&D)

CMP, Grinding and Dicing

KLA

SH/3/UR/

SUSS

**ACCRETECH**

ADT

SEMES

TORAY'

/ SH/3/UR/

## MEMORY BUSINESS IN MAINLAND CHINA

Companies active in the HBM ecosystem

# SUMMARY & OUTLOOK

- HBM is no longer just a niche product, it's at the heart of the AI revolution, and the battle for HBM leadership is becoming a strategic race on the global stage.

- HBM is reshaping the DRAM industry, capturing a growing share of the market with a projected 33% CAGR and expected to reach ~50% of DRAM revenue by 2030.

- Revenue is set to double from approximately \$17 billion in 2024 to around \$34 billion in 2025.

- Advanced bonding solutions enable higher memory stacks and seamless logic integration crucial for AI system innovation.

- China is stepping up its efforts to localize HBM production: strong domestic Al-accelerator demand, substantial government support, and an established industry network are likely to secure Chinese players a meaningful HBM foothold within the next few years.

# YOLE GROUP MEMORY PRODUCTS

### Market Monitors and Reports

**NAND Market Monitor**

**DRAM Market Monitor**

YMTC 232-layer 3D NAND

Technology, Process and Cost Reports

Next-generation DRAM 2025 - Focus on HBM and 3D DRAM

Status of the Memory Industry 2025

CXMT G4 DDR5 DRAM

Generative AI 2025

**Emerging Non-Volatile** Memory 2024 2025 edition coming soon

SK hynix HBM3

Neuromorphic Computing, Memory and Sensing 2024

Status of the Processor Industry 2025

MCU - Nuvoton M2L31 512 KB RRAM

### **ACKNOWLEDGEMENTS**

# Memory and Computing Analysts at Yole Group

Principal Analyst, Memory (DRAM)

John Lorenz

#### > Experience

15+ years in memory and computing

(Micron Technology)

> At Yole

DRAM, processors

Education

Bachelor of Science in Mechanical Engineering from the University of Illinois Urbana-Champaign (USA), with a focus on MEMS devices,

**Thibaut Grossi**

Senior Analyst,

Memory (NAND)

#### Experience

15+ in Electronic Procurement (Semiconductor, PC BA and software)

> At Yole

NAND

Education

M.Sc. in Electronic and Computing science

Simone

Bertolazzi. PhD

Principal Analyst,

Memory

#### Experience

15 years in emerging semiconductor devices

> At Yole

Memory

Education

Ph.D. in Nanoelectronics (EPFL, Switzerland)

M.Sc. in Micro & Nanotechnology

M.Sc. in Engineering Physics

Josephine Lau

Senior Analyst,

Memory

#### Experience

10+ years in memory and storage industry

> At Yole

Memory

Education

Bachelor of business marketing

Passed chartered financial analyst level

Daniel Niu

Market

Researcher

#### Experience

3+ years in memory and processor industry

→ At Yole

Memory, computing and Al

China Market

Education

Master's degree in chemical engineering

Tom

Hackenberg

Principal Analyst,

MCU

#### Experience

20+ years in computing and microcontrollers

→ At Yole

Computing

> Education

BSEE/BSECE from the University of Texas at Austin specializing in Processors and FPGAs.

Belinda Dube

Senior Analyst,

Integrated

Circuits

#### > Experience

5+ years in computing, memory and advanced packaging

#### > At Yole SystemPlus

Memory, Computing & Advanced Packaging

> Education

M.Sc. in Nanoelectronics and Nanotechnology

M.Sc. Electronics & Instrumentation

Ying-Wu Liu

Analyst, Integrated

Circuit

#### > Experience

8 years in the semiconductor industry

#### At Yole SystemPlus

Computing

#### > Education

M.Sc. in theoretical physics

M.Sc. in Integration, Security and Trust in Embedded systems

# Thank you for your attention!

Simone Bertolazzi, Ph.D.

Principal Analyst at Yole Intelligence

simone.bertolazzi@yolegroup.com