# Composable Infrastructure Leverages CXL for Memory Sharing and Benchmark Results

Brian Pan H3 Platform

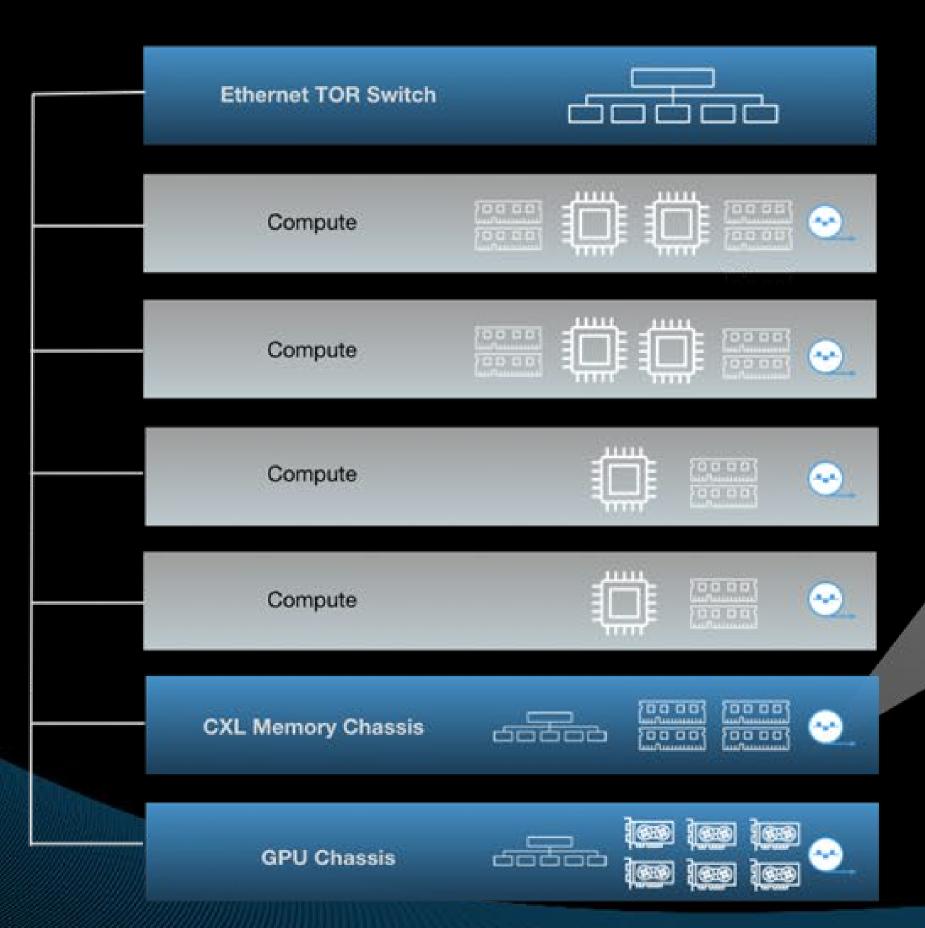

## Composable CXL Infrastructure

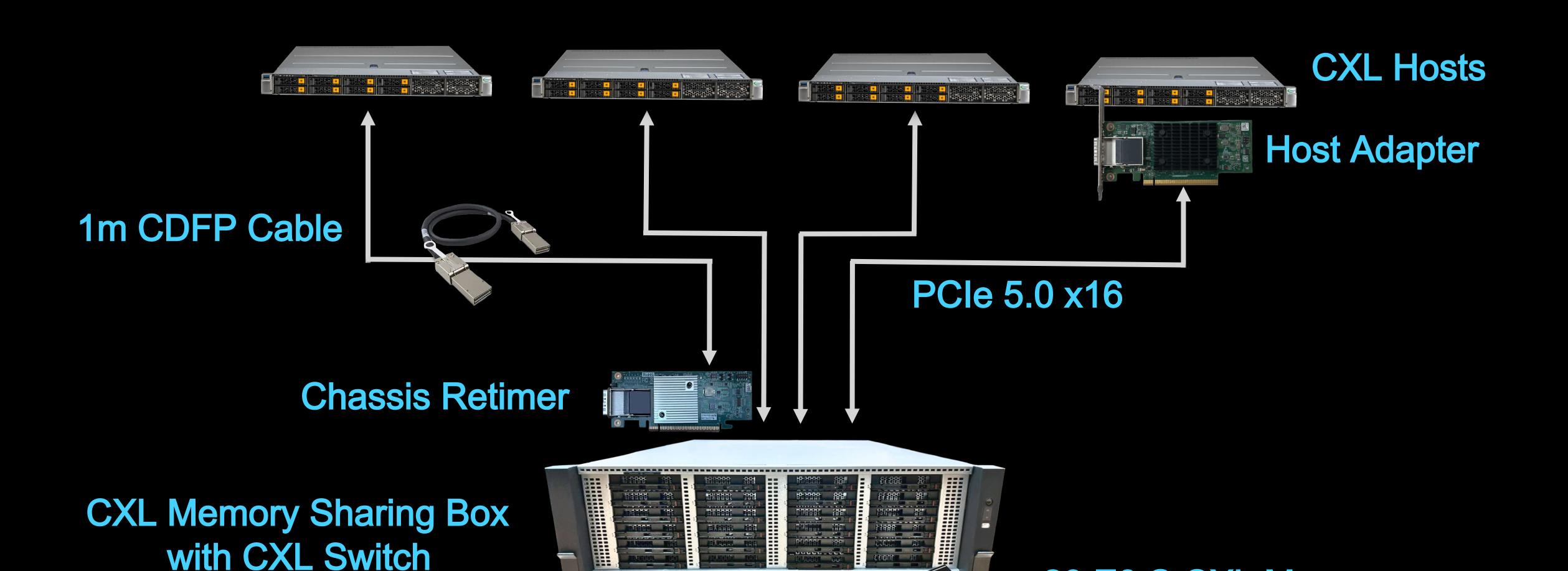

#### Physical Disaggregated Nodes

Fabric management

+

CXL switch

+

CXL Memory

### The Solution Enables Memory Sharing up to 5TB

20 E3.S CXL Memory

Modules

Note: Memory sharing without hardware cache -coherence

## Cluster Configuration

| Systems              | Configurations                                                                                                                 |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Servers              | <ul> <li>Four <u>Intel GNR</u> servers with <u>512GB DDR5</u></li> <li>One root port is connected to the CXL memory</li> </ul> |  |

| CXL Memory Appliance | <ul> <li>4 host -ports are connected to 4 different servers</li> <li>5T CXL shared memory (256GB*20)</li> </ul>                |  |

#### Configuration Consideration

- 1. The servers should have exact the same local DDR to avoid confusion.

- 2. The CXL memory modules are assigned in sequence.

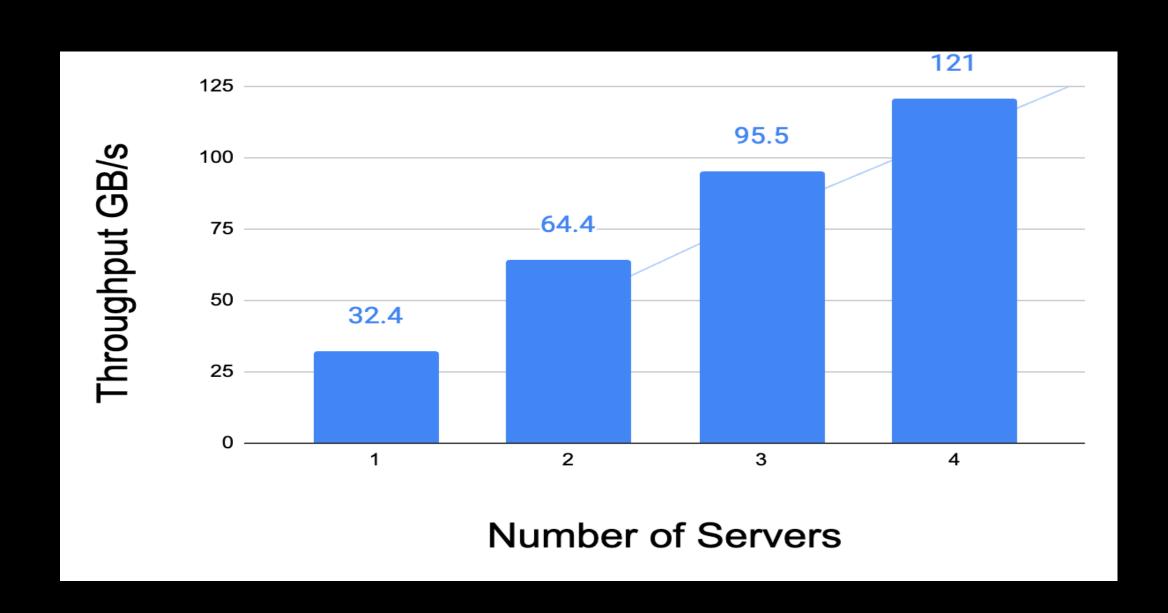

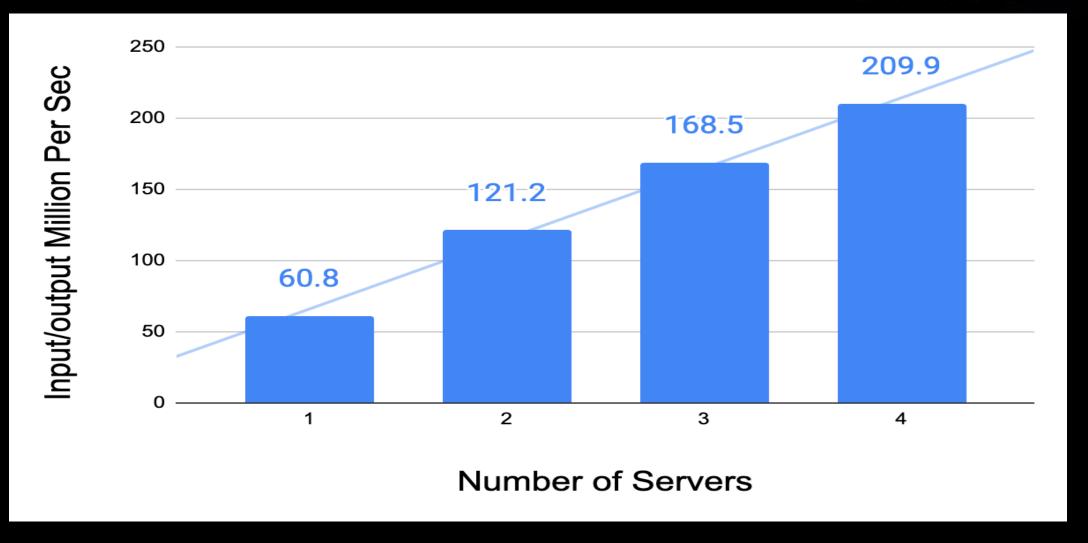

## Maximum Bandwidth 121GB/s and IOPS 210M

| Random Read            | Server 1             | Server 2             | Server 3             | Server 4             |

|------------------------|----------------------|----------------------|----------------------|----------------------|

| Server<br>DDR5#        | Intel EMR<br>32GB x2 | Intel GNR<br>64GB x1 | Intel GNR<br>64GB x1 | Intel EMR<br>16GB x4 |

| 4 servers throughput   | BW=32.4GiB/s         | BW=31.1GiB/s         | BW=32GiB/s           | BW=25.5GiB/s         |

| 4 servers Input/Output | IOPS=60.8M           | IOPS=60.4M,          | IOPS=47.3M           | IOPS=41.4M           |

| Poolmap                | 4x E3.S 256G         | 4x E3.S 256G         | 4x E3.S 256G         | 4x E3.S 256G         |

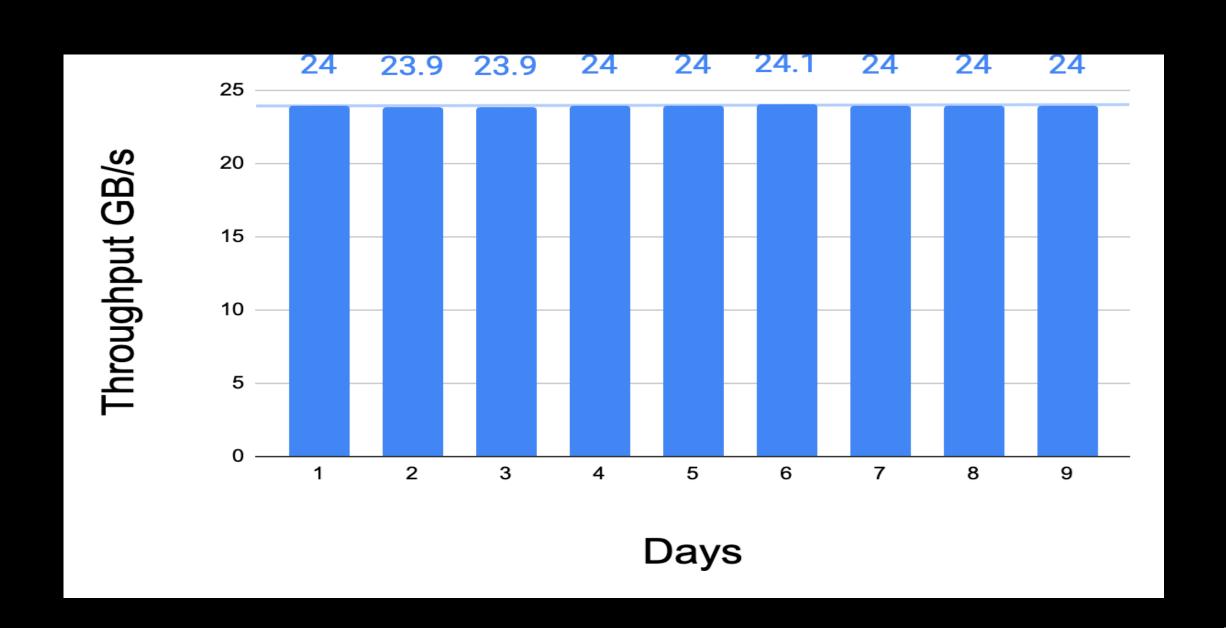

### Max perf of One CXL Sharing Memory and One Root Port

- 1.4 servers share ONE 256GB CXL memory

- 2. The throughput is 24GB/s for 9 days

- 3. Each CPU is with 128 CPU cores and each core gets 2GB memory (total 256GB)

- 4. Continuous stress to the single CXL memory for 9 days

| MLC             | Server 1                      |

|-----------------|-------------------------------|

| Server          | Intel GNR with 64GB           |

| All Read        | BW= <b>43.3</b> GiB/s         |

| 1:1 Read-writes | BW=62.1GiB/s                  |

| Poolmap         | 20x E3.S 256G(5TB CXL memory) |

## Implementation Challenges

| Items           | Description                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------|

| Server Platform | <ul> <li>Intel CXL memory address starts from 2GB</li> <li>AMD reser 12GB in 1T space</li> </ul> |

| Server BIOS     | <ul><li>CXL enabled settings</li><li>CXL memory address configuration</li></ul>                  |

| Re-timer        | Common/ SRIS clock setting                                                                       |

| CXL Driver      | OS kernel dependency                                                                             |

## Implementation Challenges

| Items                 | Description                                                                                             |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| Linux kernel          | <ul> <li>DAX and NUMA memory in Kernel 6.2</li> <li>CXL memory in Kernel 6.3 and beyond</li> </ul>      |

| Memory Error Handling | <ul> <li>Error handling and behavior of CXL switch</li> <li>CXL memory controller capability</li> </ul> |

### Call to Actions - Usage, Ecosystem, Partners

## Usage Cases from users

Deploy the suitable usage cases such as inmemory database, big data processing, HPC, AI, and so on.

## Ecosystem colloboration

Seamless integrate across multiple layers including CPU, BIOS, CXL drivers, OS, CXL memory modules work together to deploy the CXL solutions in real usage cases

#### Software partners

Build the robustic management in the existing IT systems including the memory discovery, orchestration, monitoring and analytics, trouble-shooting

Supporting

Dynamic Memory

Allocation (DCD)

Joseph Slember

**XConn Technologies**

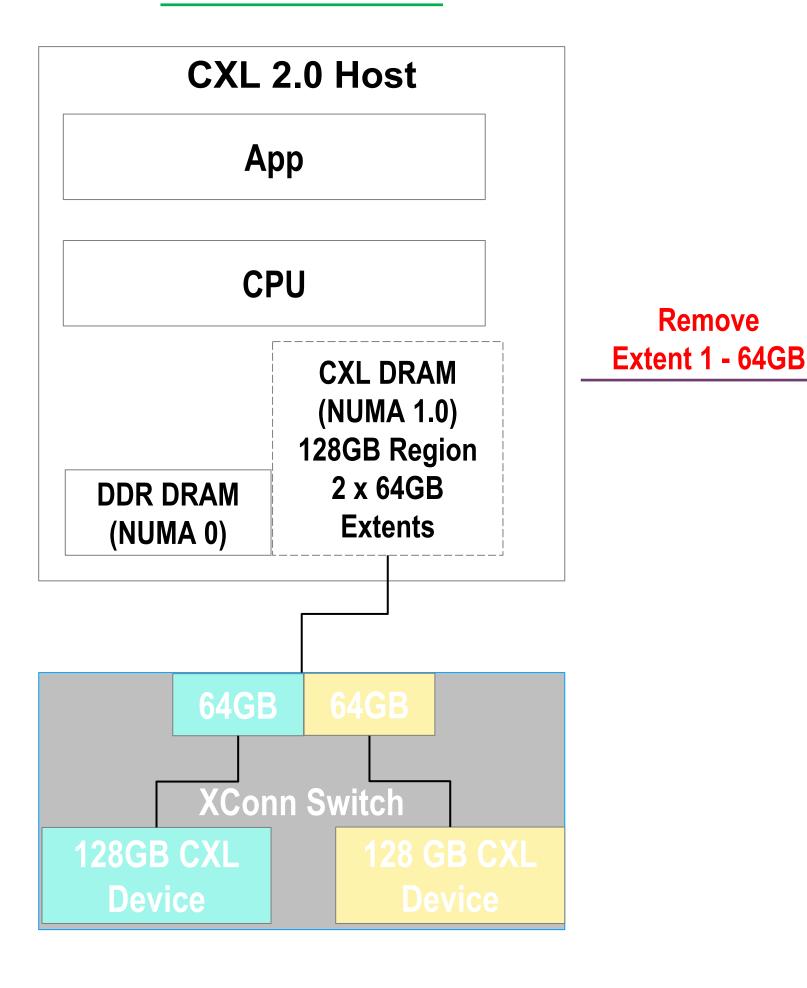

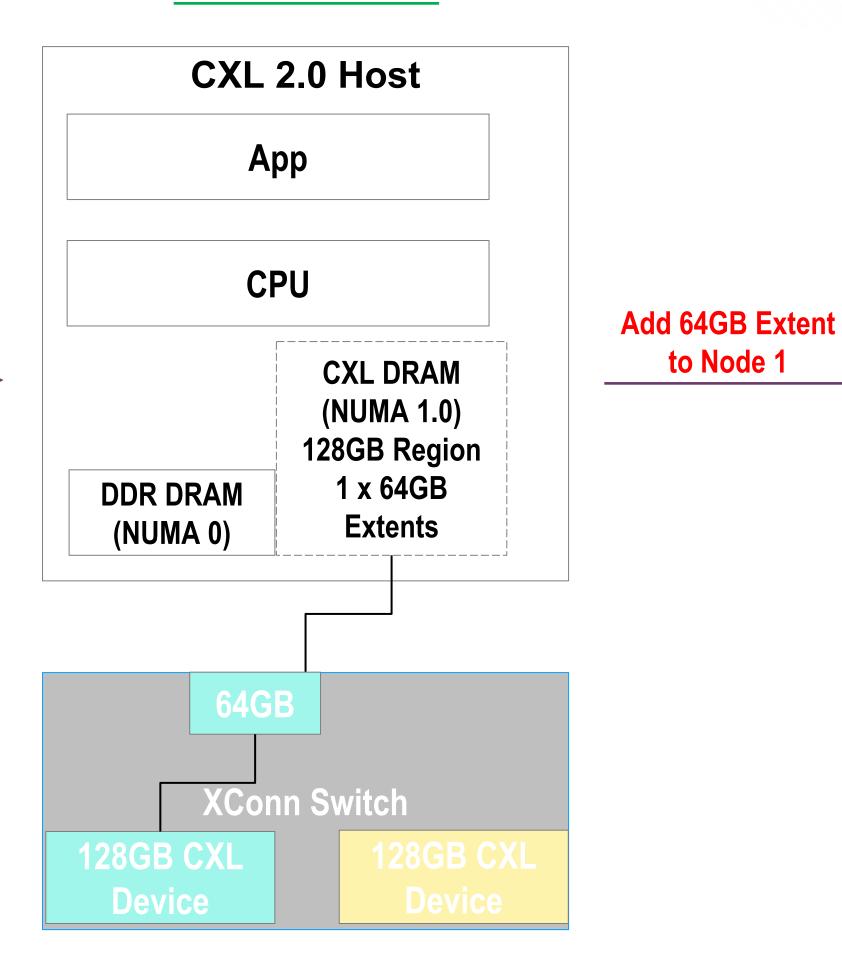

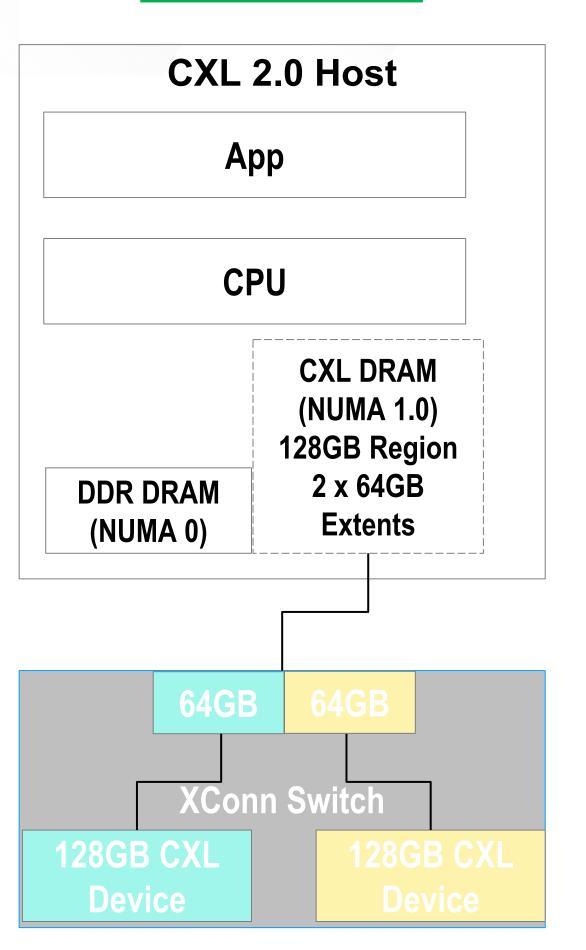

## CXL Dynamic Memory Allocation CXL

### What is Dynamic Memory Allocation?

- Ability to change how much CXL Memory is presented to a server dynamically

- Host kernel will be able to determine changes made to the memory presented without crashing

- Utilizes Dynamic Capacity Disk code in modified kernel

- CXL 3.1 Feature that can be used now

- Uses XConn Technologies Switch to export CXL Memory to a host via 2.0 Endpoint

- The Switch is able to change how much memory and from which CXL cards is presented to the host

## CXL Dynamic Memory Allocation CXL Express Link®

### What are the benefits of CXL Dynamic Memory Allocation?

- Multiple hosts can connect to the XConn CXL Switch...

- Ability to change how much CXL memory is presented to hosts on the fly as application needs change

- Ability to present different sources of CXL memory to hosts on the fly

- Enablement of MLD functionality

- Enablement of Memory Sharing and Memory Pooling without host crashing

- CXL Memory can be presented as NUMA memory or as a DAX Device

## CXL Dynamic Memory Allocation XL Express Link®

## What are the benefits of Dynamic Memory Allocation?

- Dramatically increase efficiency

- Increase application performance

- Optimize Data Center costs

- Reduce S oftware S tack

Complexity

- Disaggregation of Memory and Accelerators:

- Memory Tiering

- Scalability

- Reduced Latency

## CXL Dynamic Memory Allocation Demo CXL

Remove

#### **128GB NUMA Node**

#### **64GB NUMA Node**

to Node 1

#### **128GB NUMA Node**

## CXL Dynamic Memory Allocation Demo CXL Express Link®