# Your Chiplet Design Is Failing the UCle Spec - Here's Why

Presented by Tim Wang Lee, Ph.D.

### Navigate the EDA Complexities with a Case Study

- Why is the industry shifting to the chiplet design philosophy

- Navigate Electronic Design Automation (EDA) in chiplet designs

- EDA case study on solving chiplet signal integrity issues

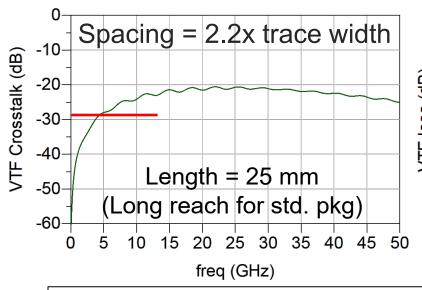

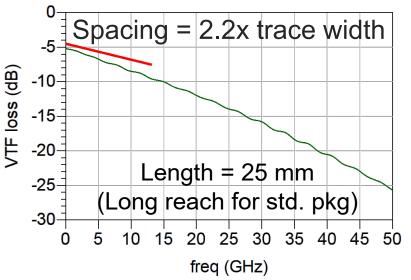

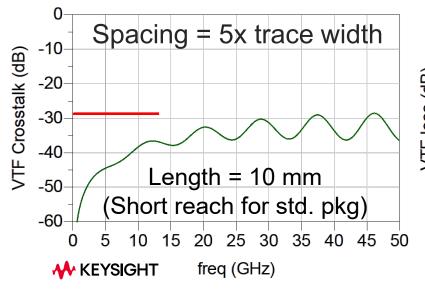

Electrical layer specifications

- Eye mask

- VTF loss

- VTF crosstalk

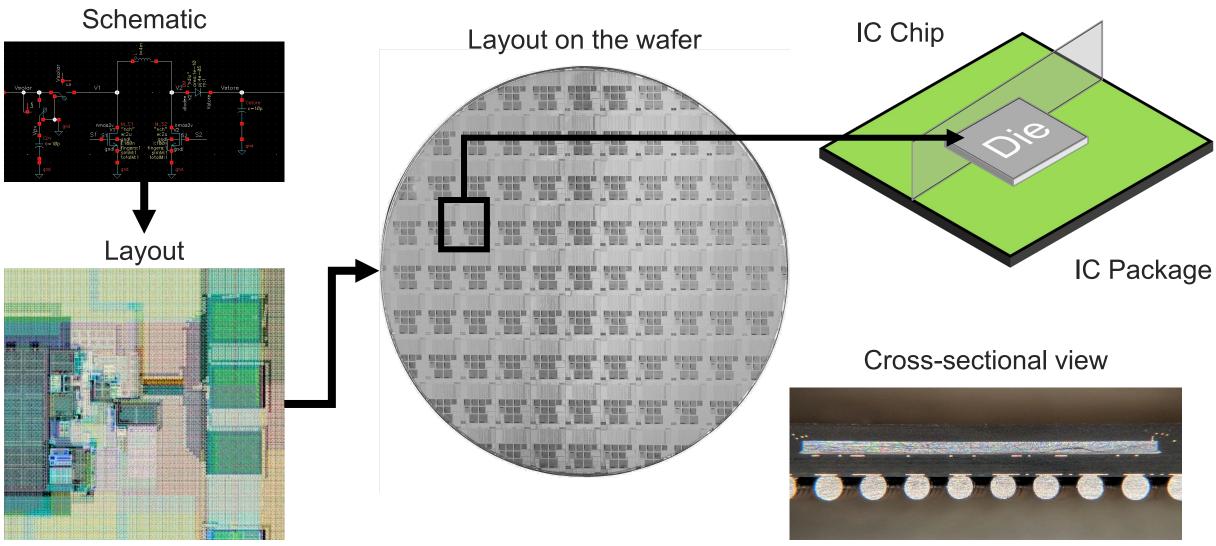

### IC Design from the Schematic, Wafer to the Package

Picture credit: <a href="https://miscircuitos.com/design-process-of-chips-asics-flow-from-design-to-tapeout/">https://miscircuitos.com/design-process-of-chips-asics-flow-from-design-to-tapeout/</a>

Picture credit: https://twitter.com/TubeTimeUS/status/1113567854698225664

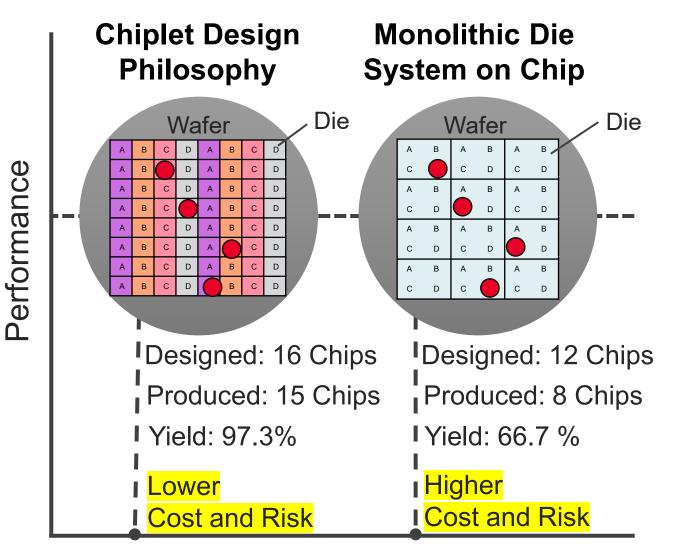

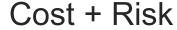

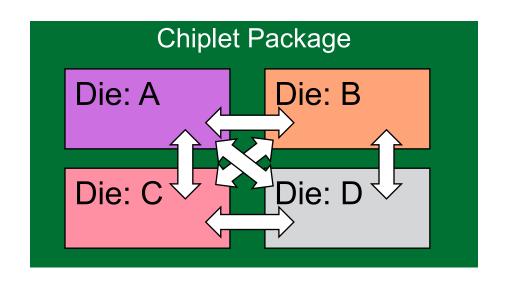

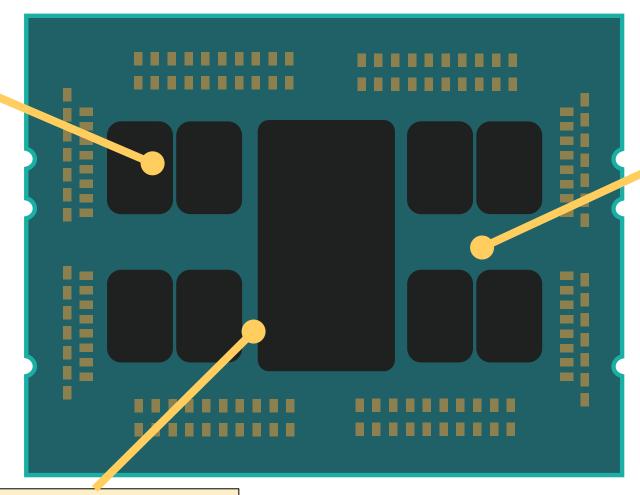

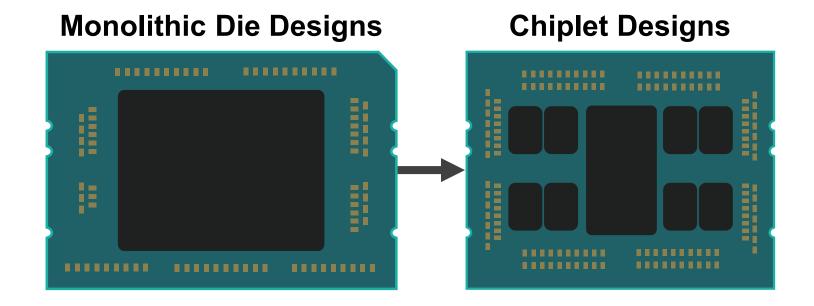

## Chiplets Improve the Cost vs. Performance of Chip Production

Monolithic approach

4 different functions in one big die

Fn: A Fn: B (CPU) (Memory)

Fn: C Fn: D (Power)

Chiplet approach

4 different dies for 4 different functions

Die: A

Die: B

Die: C

Die: D

Cost + Risk

Performance

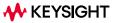

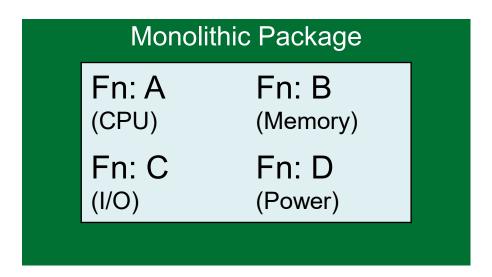

## Chiplets Improve the Cost vs. Performance of Chip Production

| Α | В | Α | В | Α | В |

|---|---|---|---|---|---|

| С | D | С | D | С | D |

| Α | В | Α | В | Α | В |

| С | D | С | D | С | D |

| Α | В | Α | В | Α | В |

| С | D | С | D | С | D |

| Α | В | Α | В | Α | В |

| С | D | С | D | С | D |

### Monolithic Die SoC

- Requires large mask (reticle) close to fabrication limit

- Has a lower yield

- Higher cost

| Α | В | С | D | Α | В | С | D |

|---|---|---|---|---|---|---|---|

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

| Α | В | С | D | Α | В | С | D |

#### Chiplet Design Philosophy

- Maximizes wafer usage

- Has a higher yield

- Has a lower cost

- Easy to scale!

The chiplet approach reduces cost, risk and improves the scaling ability.

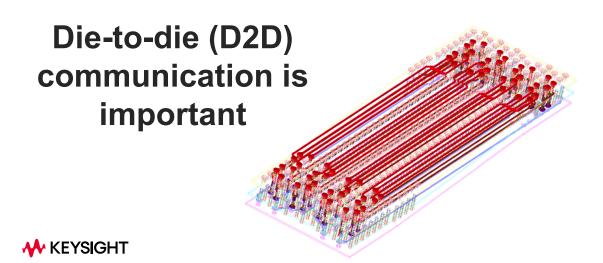

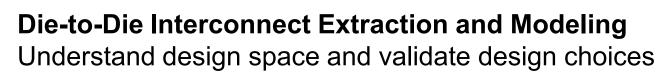

### The Catch: Die-to-Die Communication is Important for Chiplets

Various standards for the die-to-die interface between chiplets

- UCle (Universal Chiplet Interconnect express) [2]

- BoW (Bunch of Wires)

- AIB (Advanced Interface Bus)

# You Need EDA to Save Time and Money

### **EDA Software and Their Focuses in Chiplet Designs**

Goal of EDA: Predict and confirm the design's functionality and performance before physical fabrication.

#### **Schematic**

#### Circuit level simulation

- Individual circuit blocks

- Optimize and validate

### System level simulation

- Behavior between subsystems

- Analyze the signal, and power integrity

Layout vs Schematic (LVS) Verification

Layout

### Post-Layout Circuit Simulations

- Signal Integrity (SI)

- Power Integrity (PI)

- Electromagnetic Interference (EMI)

### 3 Keys to Navigate Chiplet Design Complexities with EDA

Design with chiplet standard compliance in mind

Ensure interoperability and compatibility

Exercise modular design approach

Create robust designs and remove risky dependencies

Perform complete link verification

Predict real-world behaviors and Identify issues early

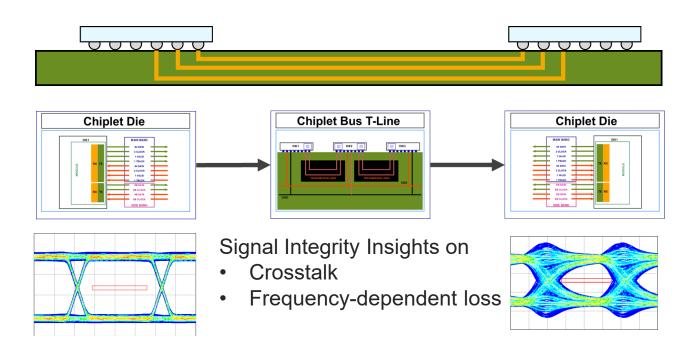

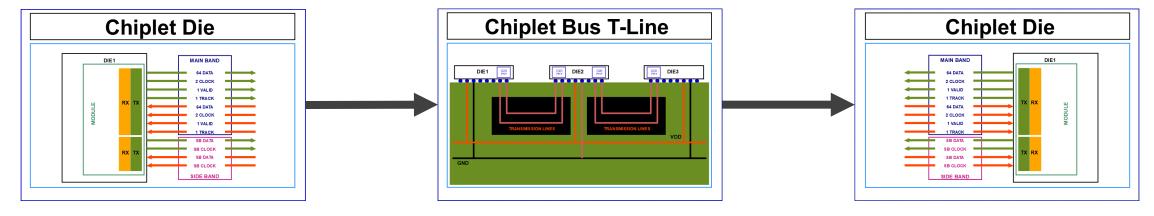

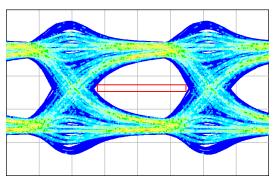

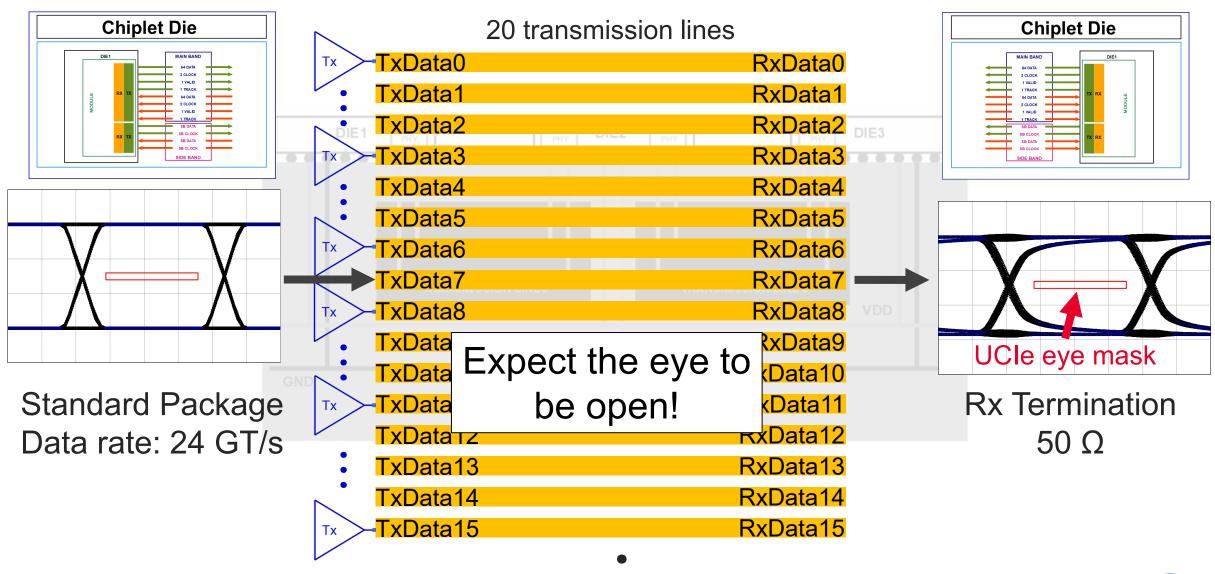

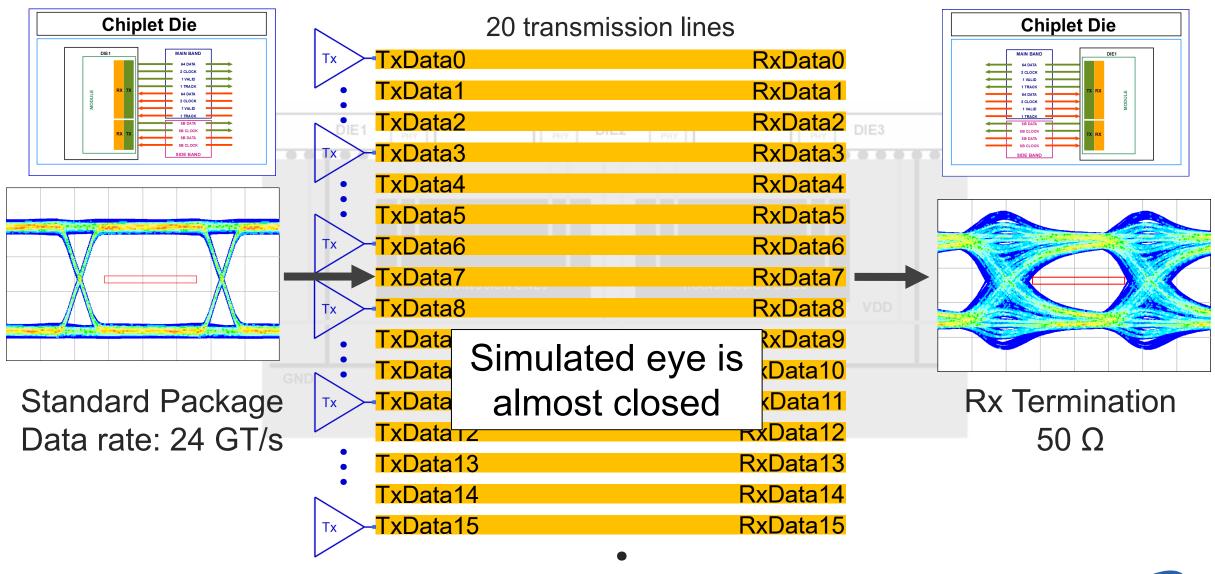

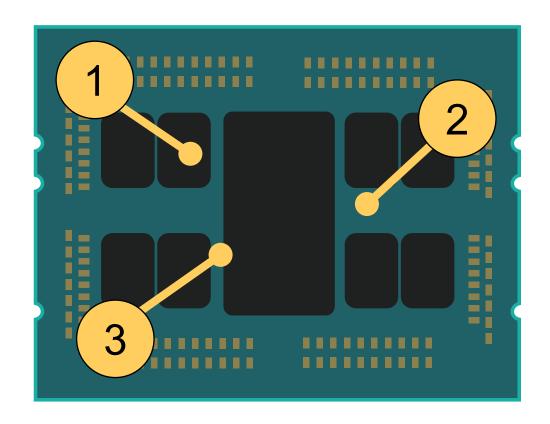

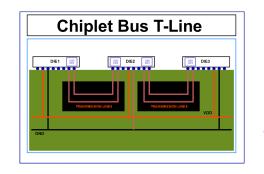

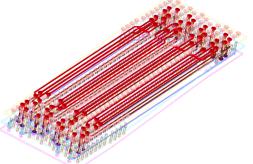

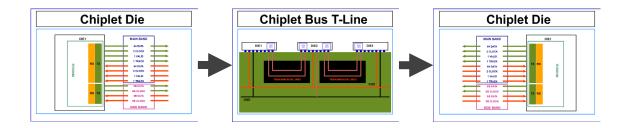

## Std Pkg UCle Link Example with Signal Integrity Insights

Signal Integrity insights on

- Crosstalk

- Frequency-dependent loss

### Rule Number 9 : Anticipate Before You Measure or Simulate

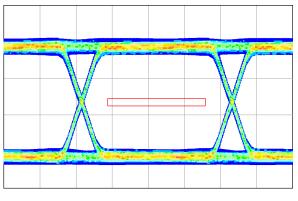

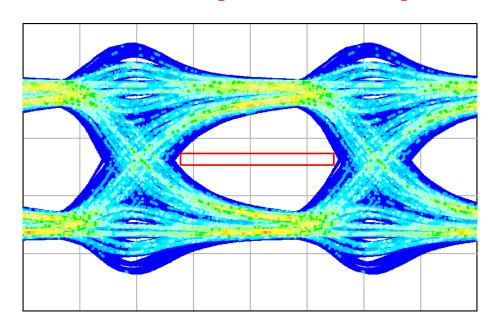

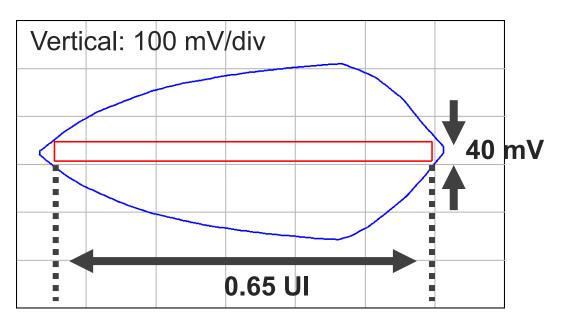

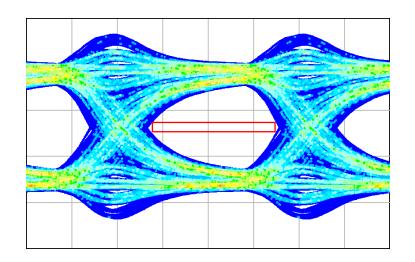

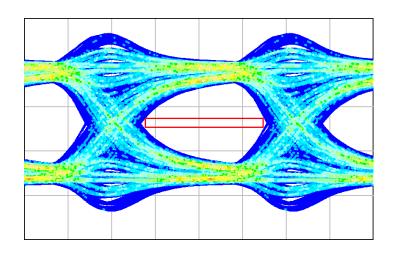

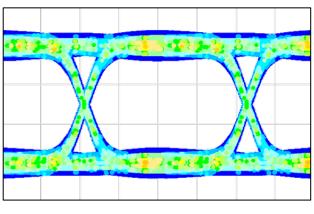

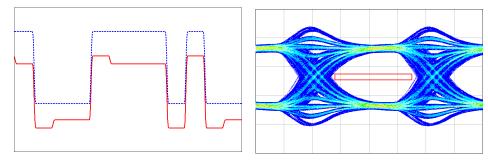

## Simulated Eye Barely Passes the UCle Eye Mask Test

### Received Eye, UCIe Eye Mask Definition, 0.2 psec Timing Margin

Standard Package Data rate: 24 GT/s

Simulation condition: **noiseless** and **jitter-less** behavioral TX and RX models

| Data Rate (GT/s)             | Eye Height (mV) | Eye Width (UI) |

|------------------------------|-----------------|----------------|

| 4, 8, 12, 16 <sup>1, 3</sup> | 40              | 0.75           |

| 24, 321,2,3                  | 40              | 0.65           |

- 1. Rectangular mask.

- 2. With equalization enabled.

- . Based on minimum Tx swing specification.

## Finding the Root Cause - Reading the Eye Diagram

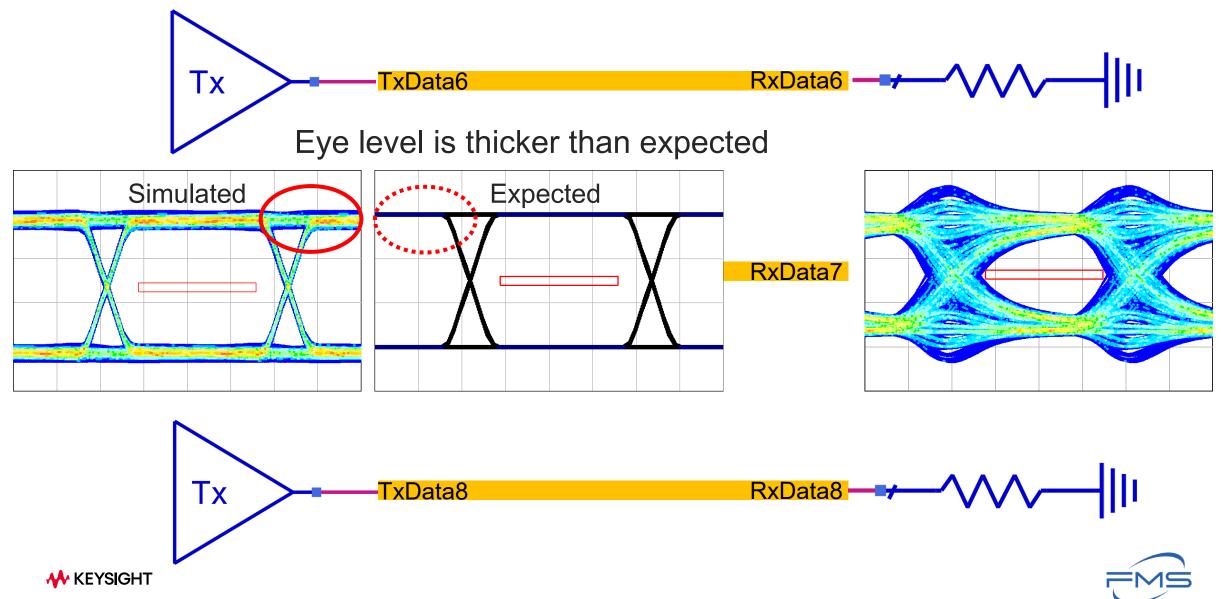

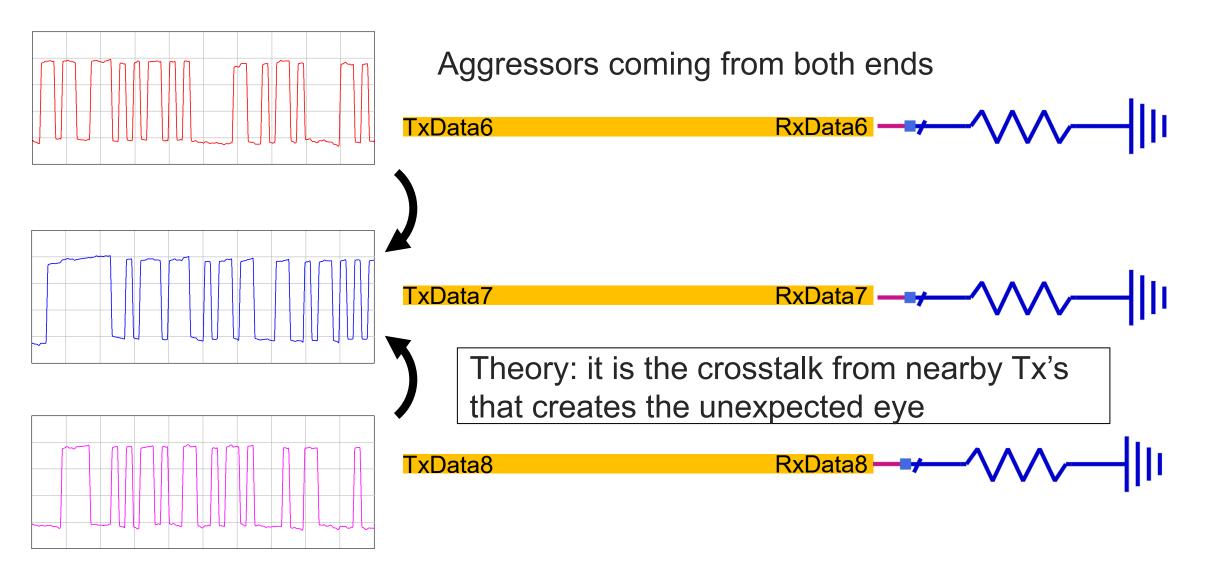

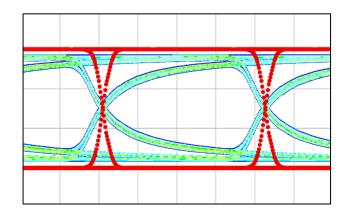

### **Nearby Channels and the Tx and Rx Eyes**

### Finding the Root Cause of Unexpected Tx Eye

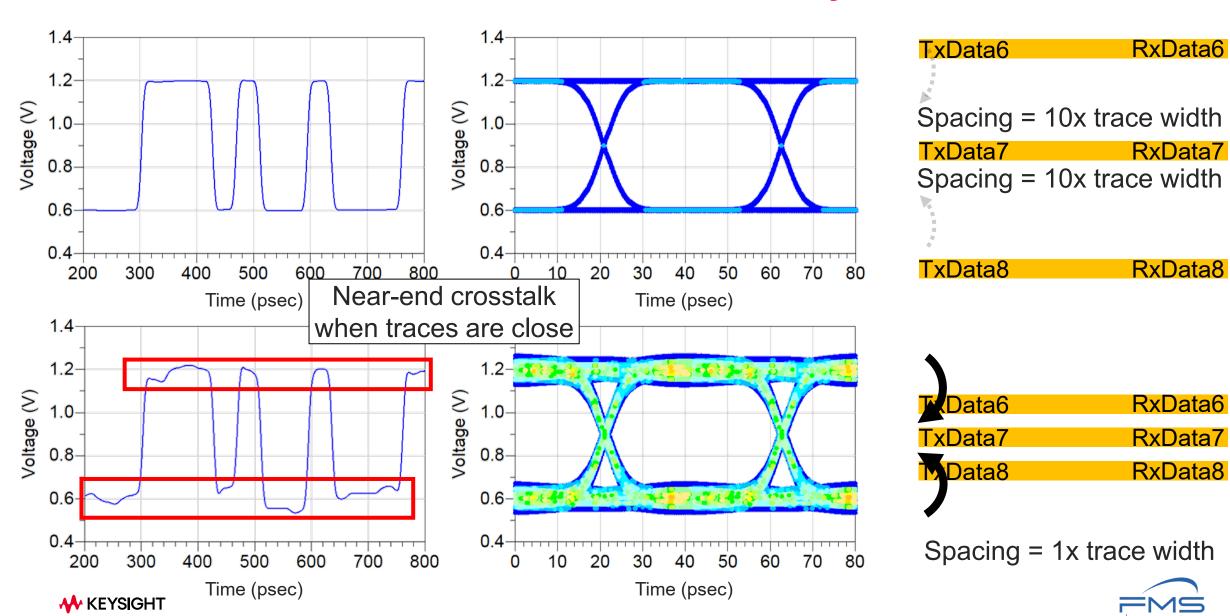

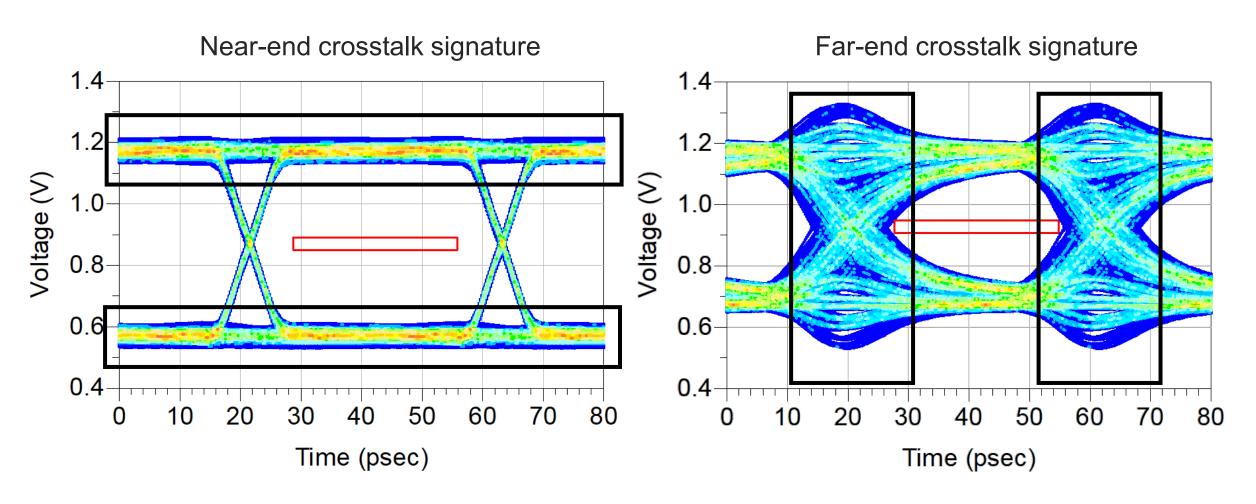

### **Confirm Near-end Crosstalk Thickens the Eye Levels**

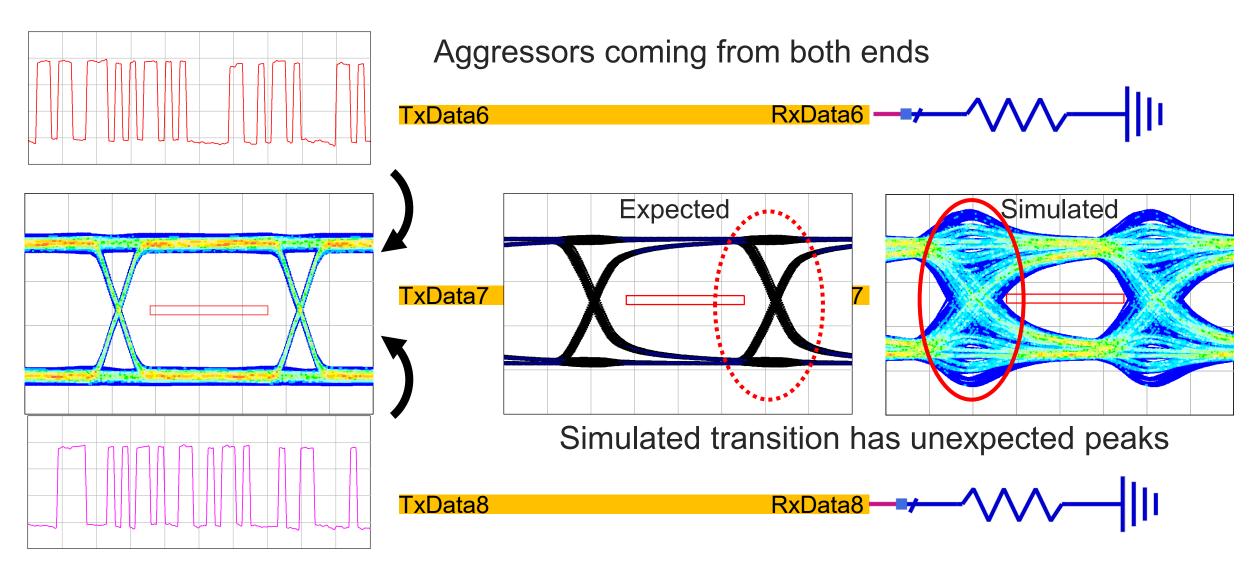

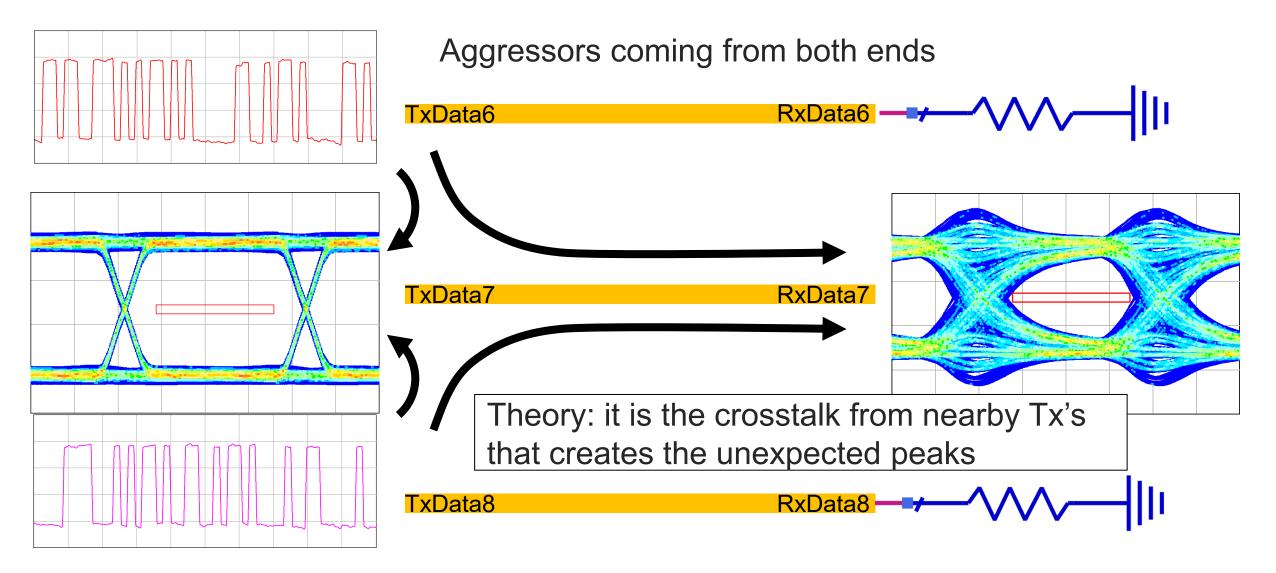

### Finding the Root Cause of Unexpected Rx Eye

### Finding the Root Cause of Unexpected Rx Eye

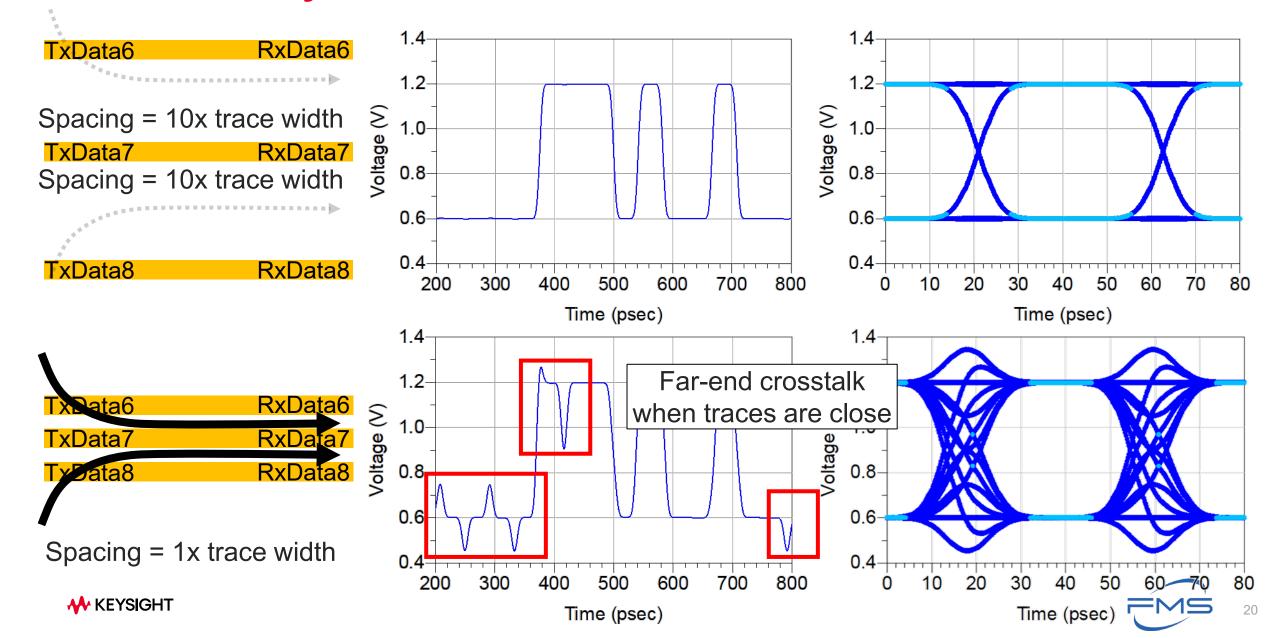

### **Confirm Rx Eye Transition Peaks When Traces Are Closer**

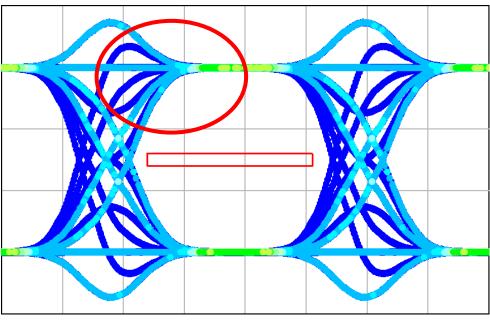

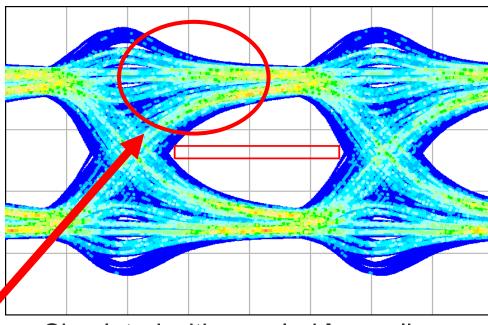

### Traces Are Close: Crosstalk Signatures in Tx Eye and Rx Eye

When the eye levels are thick and the far-end eye has peaks in the transitions, traces are likely close enough to induce near-end and far-end cross-talk.

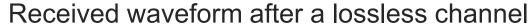

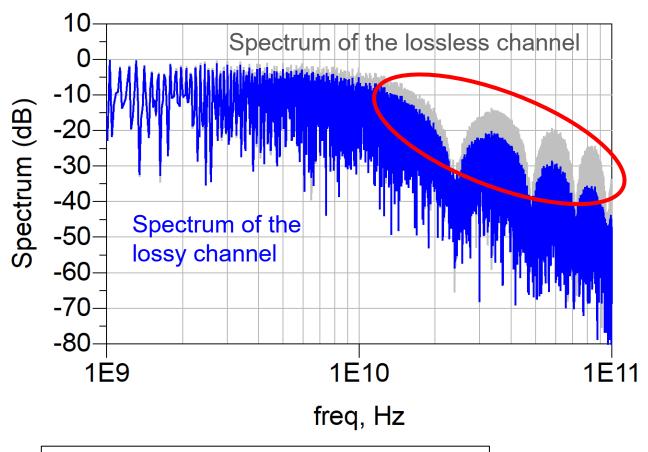

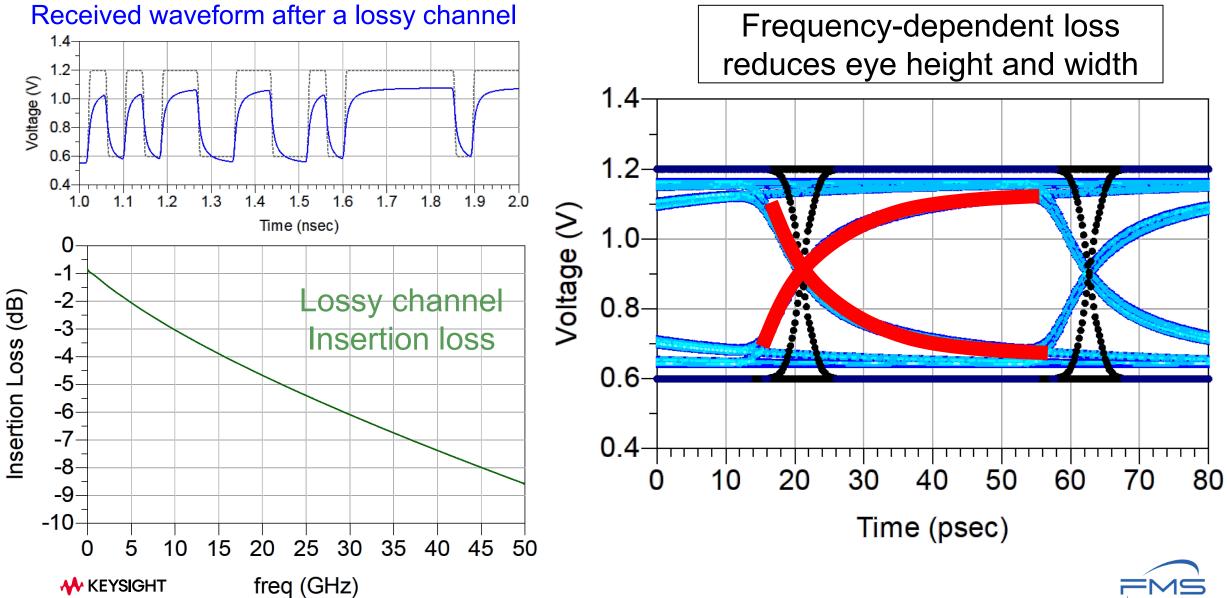

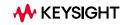

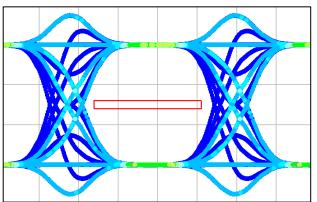

### Frequency-dependent Loss Causes Rise Time Degradation

Far-end Crosstalk Example

Simulated with coupled lossless line

Simulated Eye

Simulated with coupled lossy lines

Rise time degradation caused by frequency-dependent loss

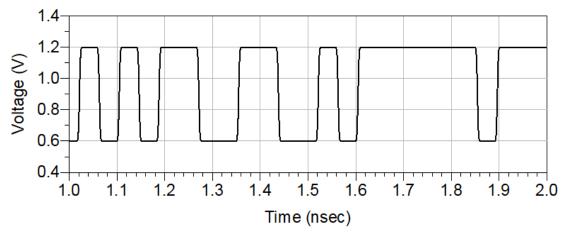

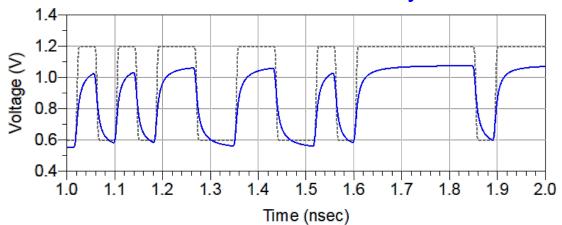

# Finding the Root Cause - Frequency-dependent Loss

### Interconnects Attenuate High-frequency Components More

### Received waveform after a lossy channel

**KEYSIGHT**

The lossy channel acts as a low-pass filter.

This low-pass filter degrades the fast rise time.

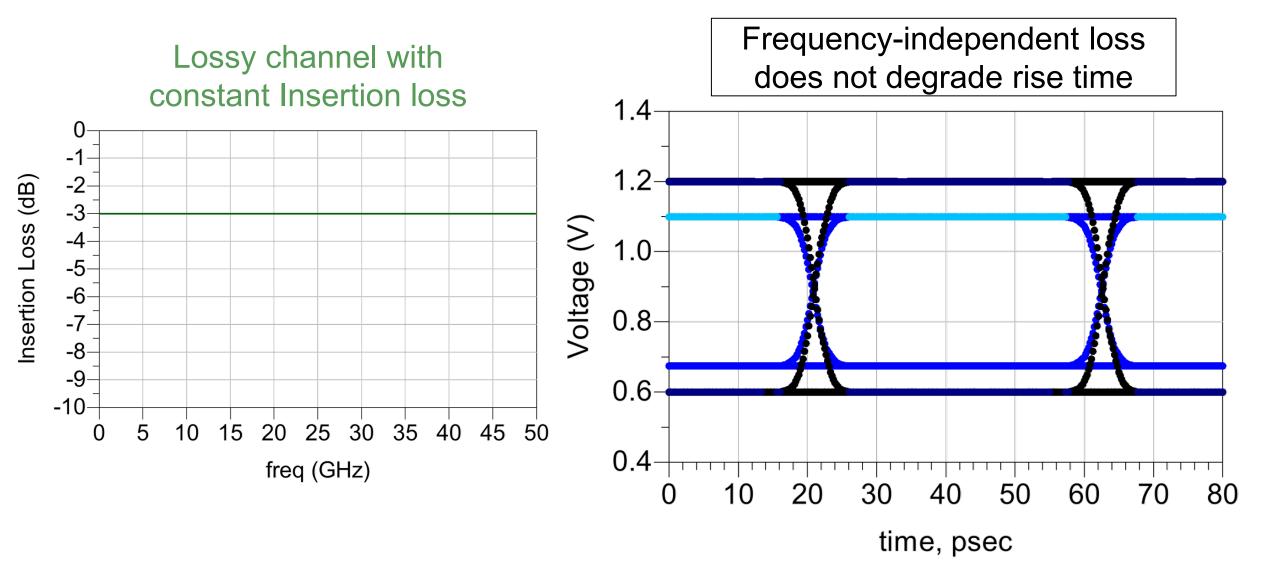

### Interconnects Attenuate High-frequency Components More

### **Constant Loss Over Frequency Only Reduces Eye Amplitude**

### **What We Have Covered So Far**

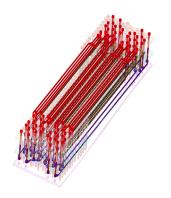

#### 20 transmission lines

| TxData0  |              | RxData0  |

|----------|--------------|----------|

| TxData1  |              | RxData1  |

| TxData2  |              | RxData2  |

| TxData3  |              | RxData3  |

| TxData4  | D2D D1E2 D20 | RxData4  |

| TXData4  |              | RXData4  |

| TxData5  |              | RxData5  |

| TxData6  |              | RxData6  |

| TxData7  |              | RxData7  |

| TxData8  |              | RxData8  |

| TxData9  |              | RxData9  |

| TxData10 |              | RxData10 |

| TxData11 |              | RxData11 |

| TxData12 |              | RxData12 |

| TxData13 |              | RxData13 |

| TxData14 |              | RxData14 |

| TxData15 |              | RxData15 |

- Eye mask

- Crosstalk signature

- Rise time degradation

## Improve the Eye by Eliminating the Root Cause

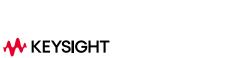

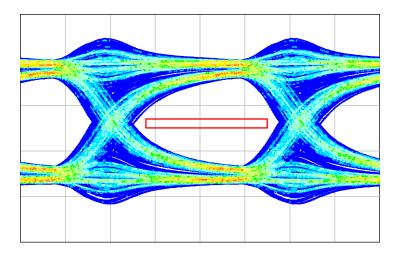

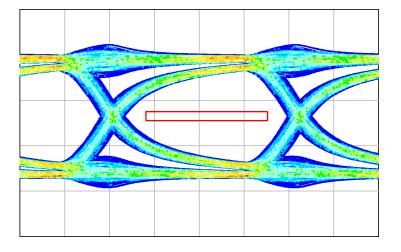

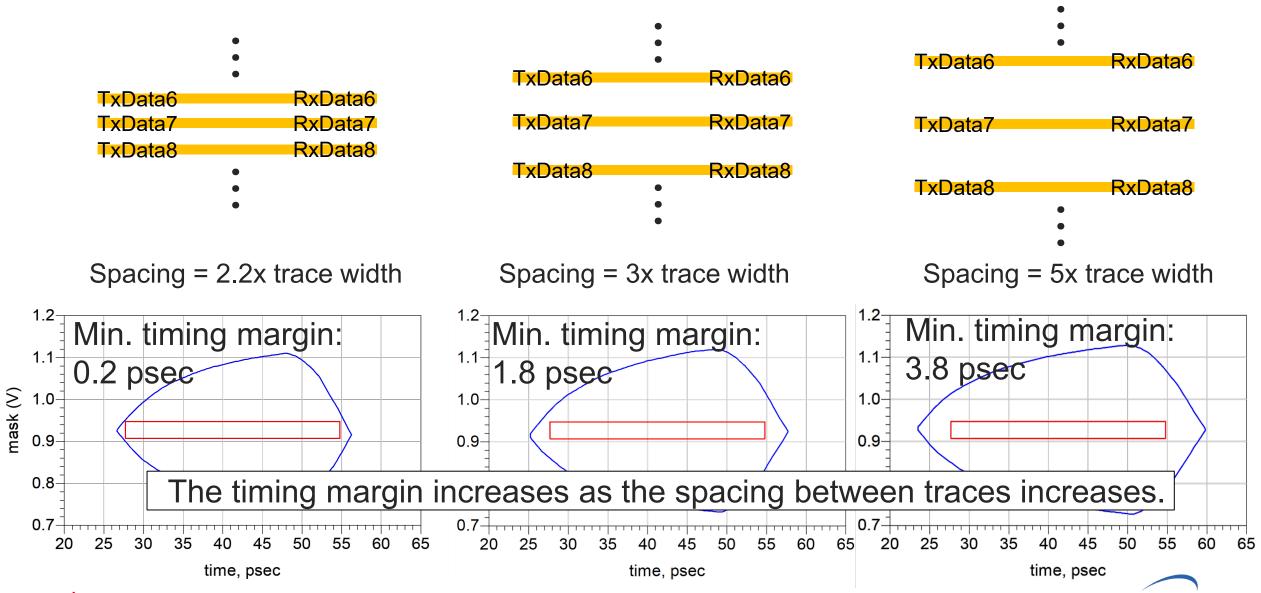

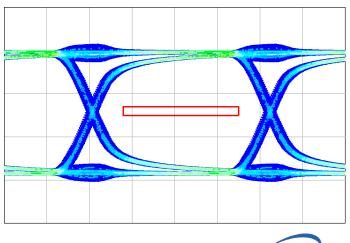

## Reduce Crosstalk by Pulling the Traces Farther Apart

## Reduce Crosstalk and Open the Eye by Increasing Spacing

TxData6 RxData6

TxData7 RxData7

TxData8 RxData8

Spacing = 3x trace width

Spacing = 5x trace width

Crosstalk reduces as spacing between traces increases.

## Increase Timing Margin by Increasing Spacing

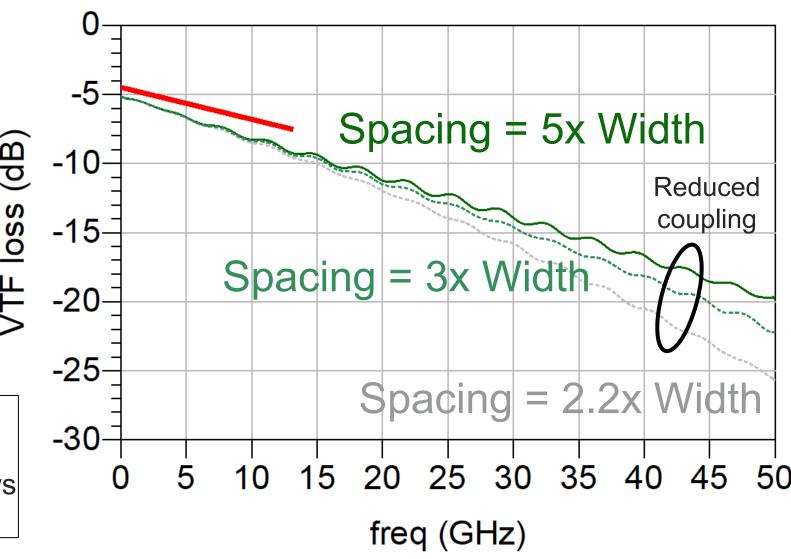

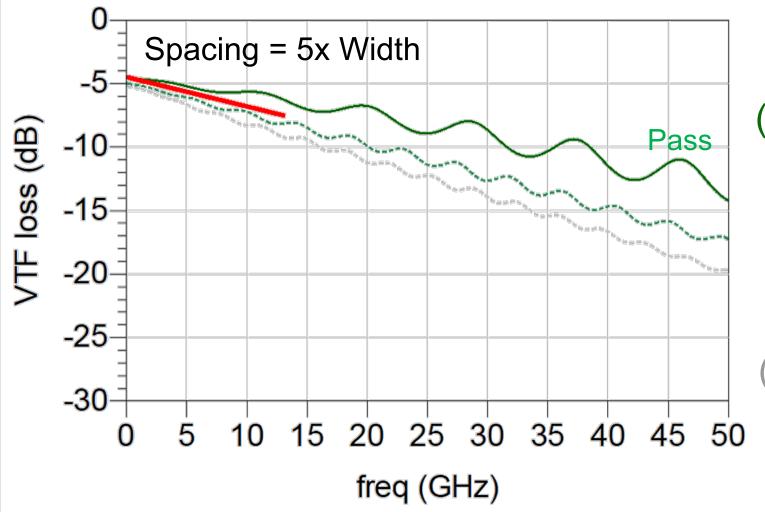

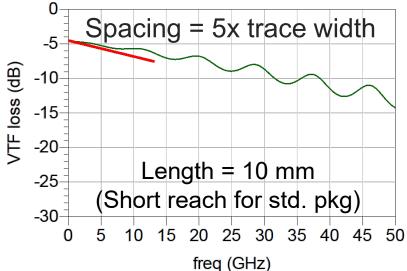

### **Expect the Increase of Spacing to Have Little Impact on Loss**

Spacing/coupling does not impact loss in general, but the impact of coupling shows up at higher frequencies.

### Shorted the Length to Reduce the Loss and Pass the Line

For the current material configuration, we can only afford a short-reach channel.

(Short reach for std. pkg) Length = 10 mm

Length = 20 mm

Length = 25 mm (Long reach for std. pkg)

### Fixing the Root Cause to Open the Eye

The eye is open after we reduced the root causes, the coupling and loss.

### **Complete the Signal Integrity Journey**

Standard Package Rx Termination 20 transmission lines Data rate: 24 GT/s 50 Ω **Chiplet Die Chiplet Die** RxData6 TxData6 TxData7 RxData7 TxData8 RxData8 Signal integrity metrics Signal integrity metrics Signal integrity metrics Tx Eye diagrams Rx Eye diagrams VTF loss

VTF crosstalk

### **Chiplet and UCle Standard Quick Recap**

### **Chiplet Design Philosophy**

- Maximizes wafer usage

- Has a higher yield

- Has a lower cost

- Easy to scale!

Standards to facilitate the adoption

## **Signal Integrity Insights Summary**

Rule number 9 [3]: Anticipate Before You Measure or Simulate

Near-end crosstalk

Frequencydependent loss

Far-end crosstalk

Reduce channel length to reduce loss

It's best to find the root cause to fix the problem!

Increase spacing to more than 3-5 times of trace width to reduce coupling.

### **Navigate Chiplet Design Simulation Complexities**

EDA is important in the design cycle to help predict the final chiplet performance

## Schematic

- Design with chiplet standard in mind

- Exercise modular design approach

- Perform complete link verification

### Key Attributes to a Chiplet D2D Comm. SI Analysis Software

Let the software work for you

Tx and Rx Termination and Equalization Explore possible design and solution space

#### **Die-to-Die Channel Link**

Identify problem early, reproduce existing problem

**Usability and Integration** Don't work for the computer

## Thank you

### References

[1] G. Loh, "An Overview of Chiplet Technology for the AMD EPYC™ and Ryzen™ Processor Families," [Online Video], Available: <a href="https://youtu.be/wqRAG\_5KzBE">https://youtu.be/wqRAG\_5KzBE</a>.

[2] "Universal Chiplet Interconnect Express (UCIe) Specification," July 10, 2023, Revision 1.1, Version 1.0.

[3] E. Bogatin, "Bogatin's 20 Rules for Engineers," Signal Integrity Journal, [Online]. Available: <a href="https://www.signalintegrityjournal.com/blogs/4-eric-bogatin-signal-integrity-journal-technical-editor/post/1539-bogatins-20-rules-for-engineers">https://www.signalintegrityjournal.com/blogs/4-eric-bogatin-signal-integrity-journal-technical-editor/post/1539-bogatins-20-rules-for-engineers</a>.