# A Distributed Controller for Flexible Applications in the AI Era

Nick.Huang

**Supervisor Engineer**

Silicon Motion Technology Corp.

# Agenda

- Latest NAND Technology

- The AI Challenge

- Controller Innovation: Meeting New Demands

- Looking Ahead: The Future of NAND in the Al Era

## **Overview**

- NAND flash memory is a core component in modern storage systems.

- NAND interface speeds are rapidly evolving.

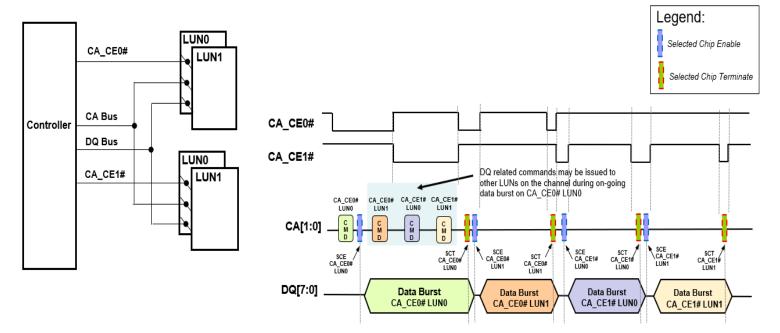

ONFI 5.1 update and its key innovation—the Separate Command

Address (SCA) protocol

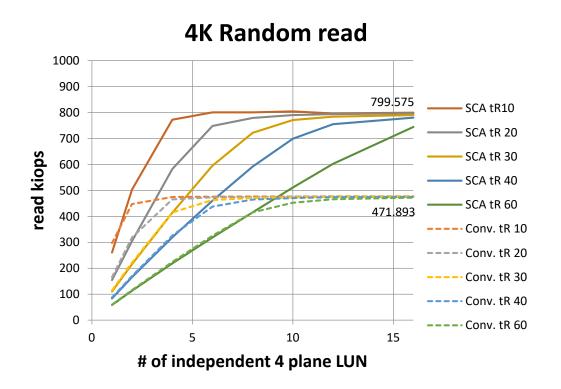

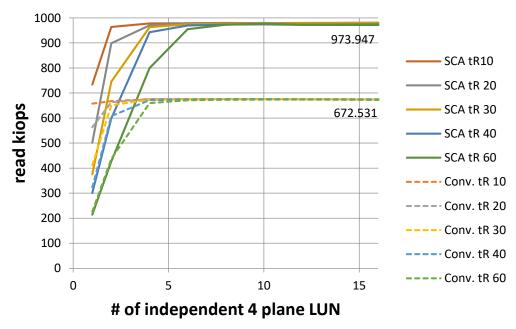

## **Comparison SCA and Conv. at DDR4800**

### **16K Sequential read**

# **Current Challenges in the NAND Industry**

- AI workloads demand more flexible and high-performance storage solutions

- Massive Data Throughput

- Parallel Access & Scalability

- High-Capacity & Tiered Storage

- Inference Optimization

# **Current Challenges in the NAND Industry**

- Critical Pain Points in NAND Technology

- Performance Bottlenecks

- Signal quality

- Energy consumption

Excoural Conslongy Frediedstion

Energy Consumption dealvation

# **Current Challenges in the NAND Industry**

- Increased Performance and Scalability

- Enhanced Signal Integrity

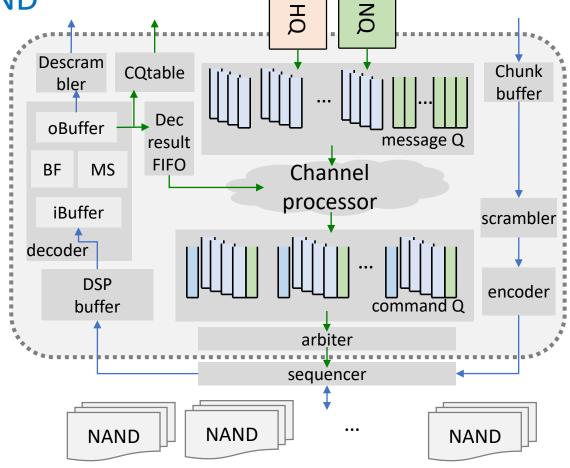

## **Controller Innovation: Meeting New Demands**

- Parallelism and Channel Scaling

- Intelligence

- QoS & Latency Management

- Compute-in-Storage (CIS) / Computational Storage

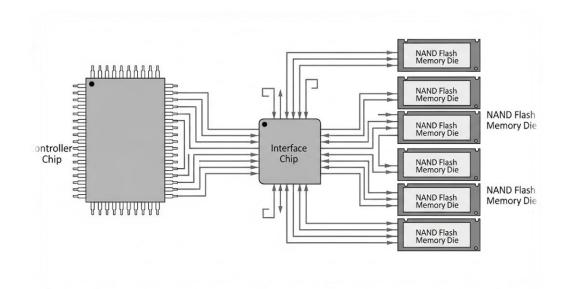

# A simple architecture of FPU

- Take care all dirty works of NAND

- Error retry

- Media healthiness

- Transparent and error free access

- Physical address access

- Low latency

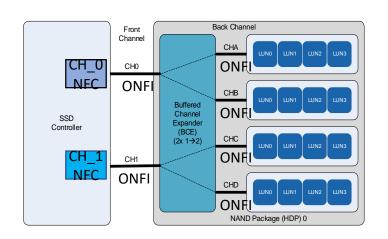

## **Distributed Controller**

#### **DPU**

#### NVMe, FTL, GC, Near data process

#### Example

- SerDes / PCle switch

- Compression/deduplication

- Al inference accelerator

...etc

#### **FPU**

#### **Transparent Error-free NAND access**

#### Example

- Enterprise FPU

- Specialized sequential read FPU

- FPU w/ 512B for GPU IO

...etc

- Flexibility

- 4CH mainstream => DPU + 4CH FPU

- 8CH performance => DPU + 4CH FPU x 2

- Efficient data transfer, power saving

- coded data on ONFI (w/LDPC parity) => data (w/o LDPC parity) on SerDes.

- Better thermal distribution

- Fault tolerant (e.g. DPU 12nm, FPU 6nm), Zig-Zag update.

- Highly customizable: DPU x FPU

# **Buffer chip V.S. FPU**

| Feature           | Analog Switch                           | Re-driver                                       | Re-timer                                                          |

|-------------------|-----------------------------------------|-------------------------------------------------|-------------------------------------------------------------------|

| Function          | Routes/selects analog signals           | Amplifies and equalizes degraded analog signals | Fully regenerates digital signals (data + clock)                  |

| Signal Type       | Analog                                  | Analog (with equalization for digital signals)  | Mixed-signal (analog front-<br>end, digital regeneration)         |

| Protocol<br>Aware | No                                      | No                                              | Yes                                                               |

| Jitter Handle     | no active compensation                  | Compensates for deterministic jitter (ISI).     | Compensates for both ISI and random jitter, resets jitter budget. |

| Noise Impact      | Can introduce minimal noise/attenuation | Amplifies existing noise, can add its own noise | Removes noise, retransmits a clean signal                         |

| Complexity & Cost | Low                                     | Medium                                          | High                                                              |

| Timing Delay      | Minimal added delay                     | Some propagation delay                          | Large delay due to regeneration pipeline                          |

| Use Case          | NA                                      | Conventional protocol                           | Conventiona + SCA                                                 |

#### **FPU direct sub-channels**

Integrates signal conditioning & protocol handling in controller.

Mixed-signal (analog PHYs, digital logic for protocol/timing)

**Full Protocol Awareness**

**Optimal Jitter Control**

Minimized by design

No extra chip, higher design cost

internal pipeline delays

Conventional + SCA w/o additional latency

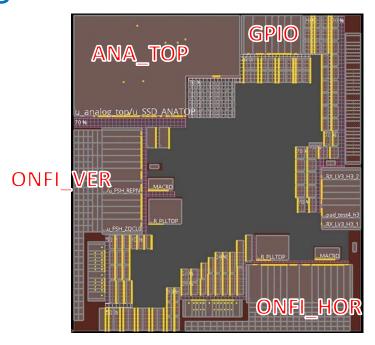

## **FPU Test Chip**

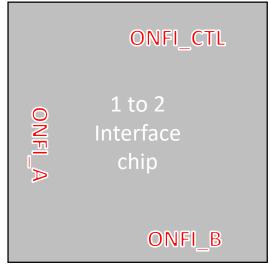

SMI FPU chip with two ONFI interface can double data bandwidth with NAND die use TSMC shuttle to make a silicon prove at end of 2025

Why not utilize it better?

## Looking Ahead: The Future of NAND in the Al Era

### Trends and Vision:

Continued evolution of chiplet technology

## • Al Everywhere:

From cloud to edge, AI is driving new storage demands.

## Intelligent Storage:

Controllers will evolve to become smarter and more autonomous.

## Collaboration:

Stronger partnerships between NAND vendors and AI platform providers.

## Next Steps:

Expand support for emerging NAND technologies.

Deep integration with AI frameworks and hardware.

## **Legal Notice and Disclaimer**

- The content of this document including, but not limited to, concepts, ideas, figures and architectures is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Silicon Motion Inc. and its affiliates. Silicon Motion Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this document.

- Nothing in these materials is an offer to sell any of the components or devices referenced herein.

- Silicon Motion Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from Silicon Motion, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

- © 2025 Silicon Motion Inc. or its affiliates. All Rights Reserved.

- Silicon Motion, the Silicon Motion logo, MonTitan™, the MonTitan™ logo are trademarks or registered trademarks of Silicon Motion Inc.

Meet us at booth #315

Scan to learn more!

Scan to learn more!

# Meet us at booth #315

Smart Storage in Motion: From Silicon Innovation to Al Transformation Across all Spectrums!