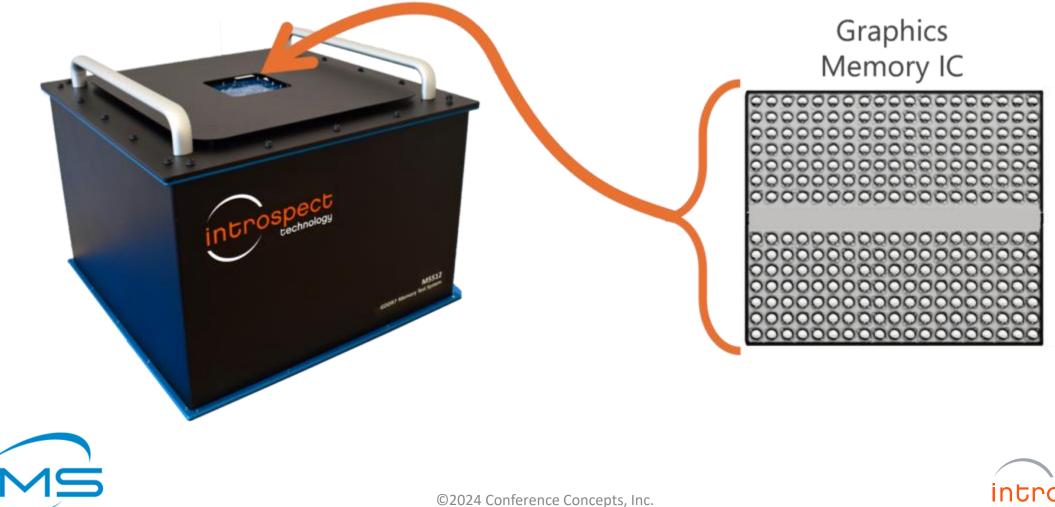

## Design of a 72-Channel, 40 Gbps PAM3 ATE-on-Bench Test System for GDDR7 Memories

Erin Holley and Mohamed Hafed

Introspect Technology

## The GDDR7 Specification

#### A major step forward...

- 1 Tbps throughput on a single memory device

- 64 Gbit of storage on a single memory device

# The GDDR7 Specification **A major step forward...**

- 1 Tbps throughput on a single memory device

- 64 Gbit of storage on a single memory device

#### An unprecedented testing challenge...

- How to perform BERT-based I/O characterization

- How to perform memory cell testing

#### Focus of This Presentation Design of an ATE on Bench Solution for GDDR7

All Rights Reserved

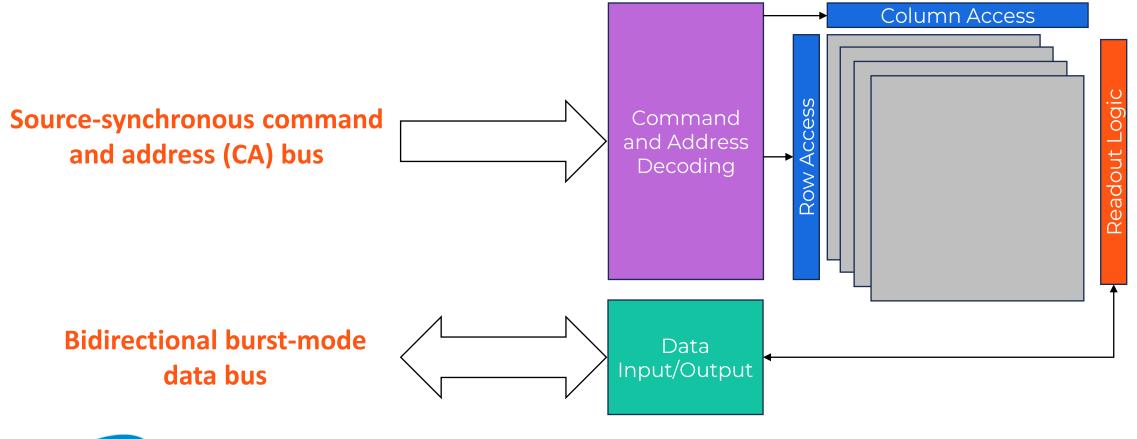

# Overview of the GDDR7 Specification It still looks like a DDR memory interface

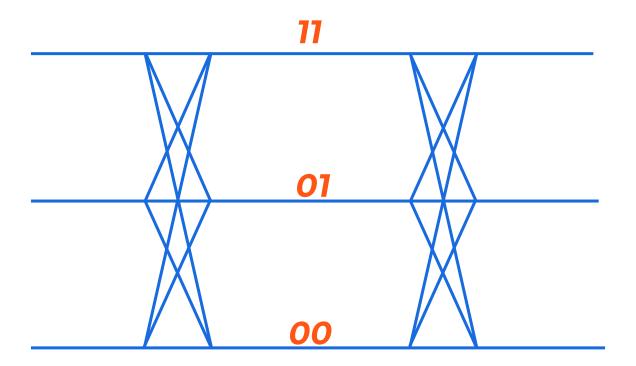

# Overview of the GDDR7 Specification It introduces PAM3 signaling

- Ethernet, USB, or PCIe are all high-speed, but they rely on <u>differential signaling</u>

- The GDDR7 DQ pins are all single-ended, and this requires more careful design

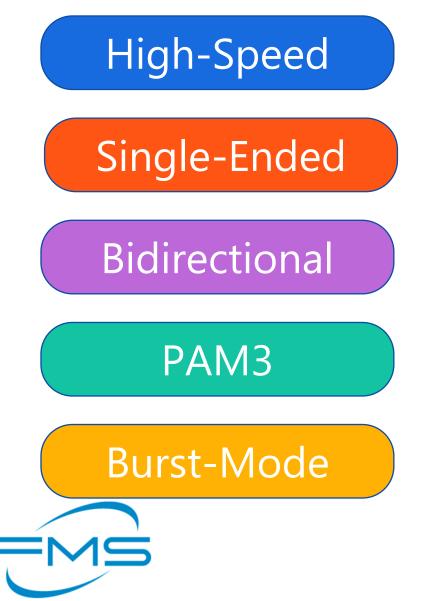

### High-Speed

#### Bidirectional

Single-Ended

### PAM3

- Ethernet, USB, or PCIe all have <u>separate Tx and Rx</u> lanes, so the PHY implementation does not require bidirectional I/Os

- The GDDR7 DQ pins are all bidirectional I/Os, and this is a major design challenge

- Ethernet, USB, or PCIe all rely on CDR-based SerDes (with <u>continuous data</u>)

- The GDDR7 interface is burst-mode with very short burst sizes. So, it is not possible to use a CDR

Single-Ended

Bidirectional

#### PAM3

#### Burst-Mode

©2024 Conference Concepts, Inc. All Rights Reserved

#### **GDDR7 poses significant** <u>electrical</u> test and characterization challenges

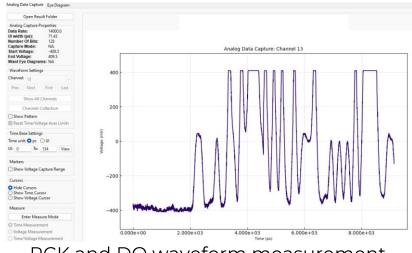

#### CA Bus Training

- Drive CA and measure DQ

- Drive CA, DQ and measure DQ

- DQ has both write and read training

### CA Bus Training

#### DQ Bus Training

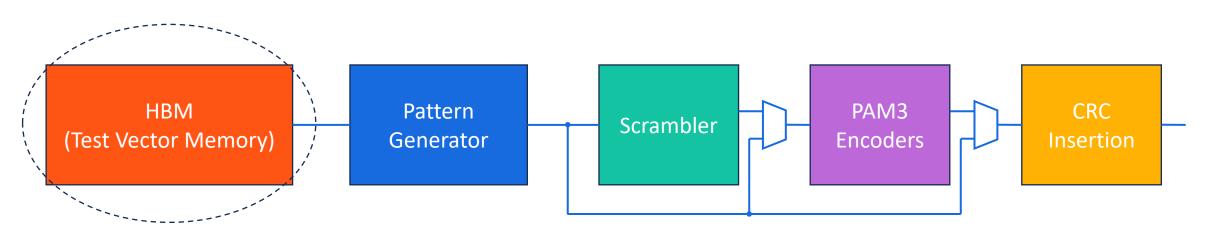

### PAM3 Encoders

- <u>Three</u> different PAM3 encoders (11b7s, 3b2s, 2b1s)

- PAM3 encoders are distributed across lanes

### CA Bus Training

### DQ Bus Training

#### PAM3 Encoders

#### Data Integrity

- CRC on read/write transfers

- ECC on read/write transfers and on-die memory cells

- Command address parity

CA Bus Training

DQ Bus Training

PAM3 Encoders

Data Integrity

## GDDR7 poses significant protocol test and characterization challenges

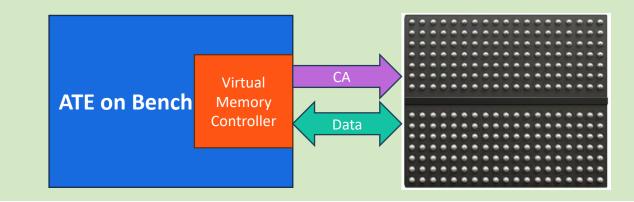

#### Design of the ATE on Bench Solution Parallel, Protocol-Aware BERT & Functional Memory Tester...

### Goals of the Design

#### **PHY Level Testing and Characterization**

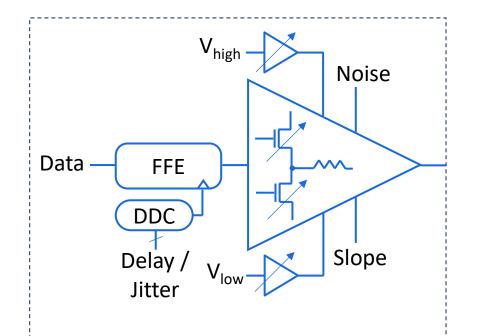

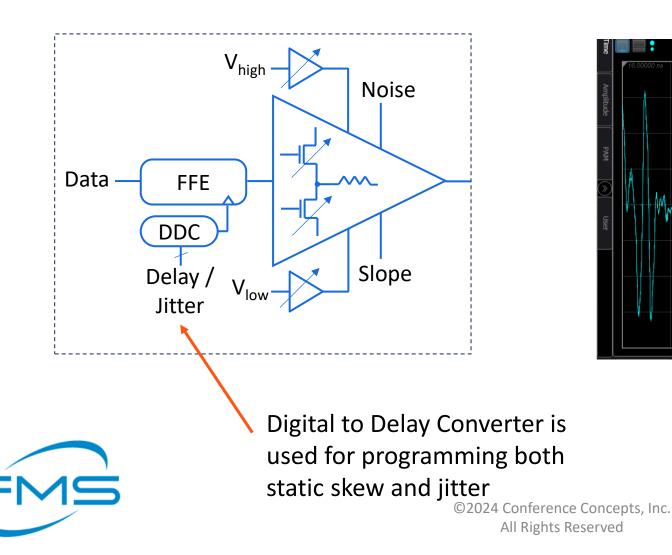

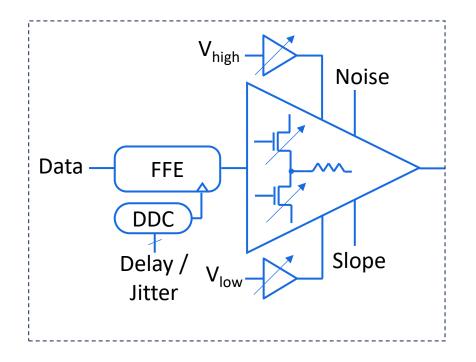

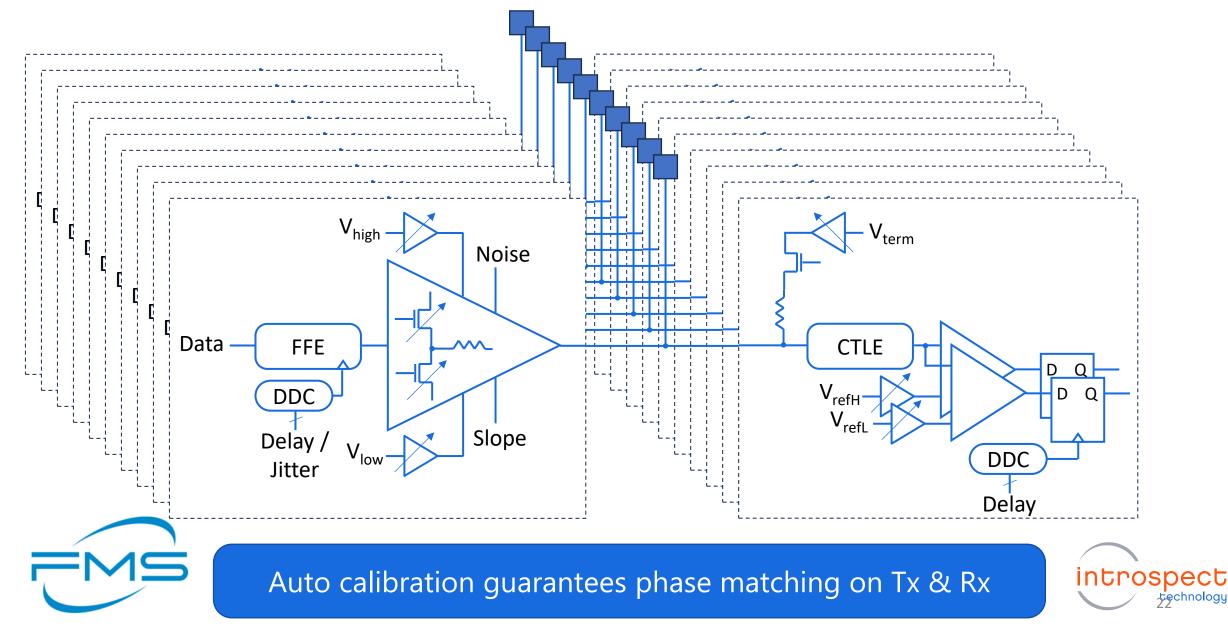

Adjustable voltage and timing parameters on all pins (including jitter injection)

Act as a high-performance, parallel, protocol-aware BERT

#### **Virtual Memory Controller**

Act as a CPU/GPU memory controller Protocol-compliant stimulus for all memory commands

#### **Functional Stress Testing**

What are the limits of the device? Verify functional behavior while pushing command timings,

data rate and other parameters out of spec

introspect

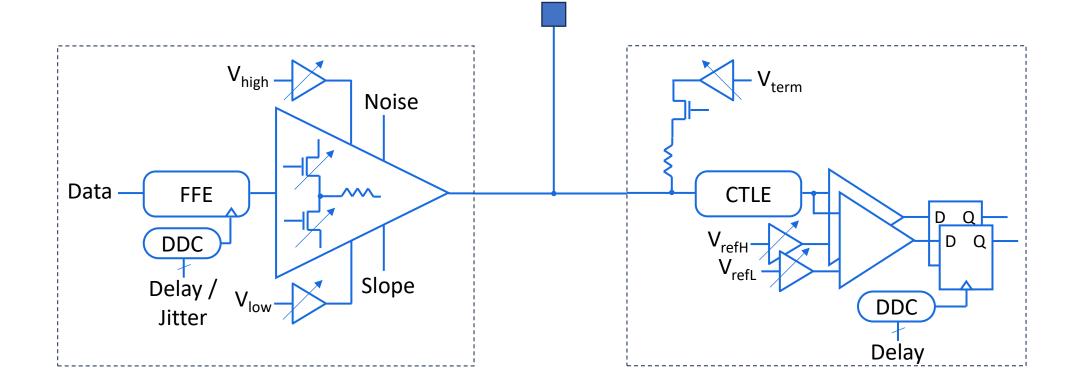

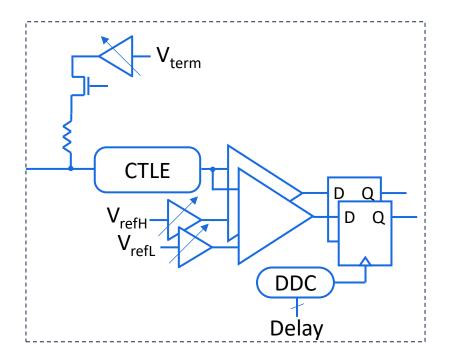

#### Pin Electronic Design

introspect

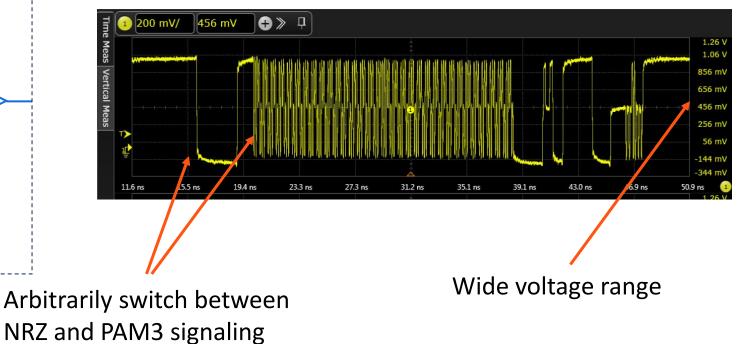

### Pin Electronic Design – Cycle Level Control

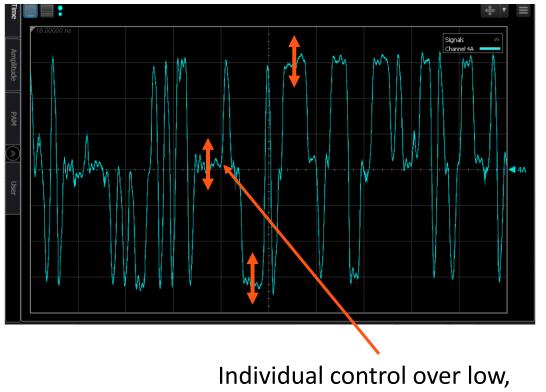

#### Pin Electronic Design – Impairments

mid, and high voltages

### Pin Electronic Design – Designed for 40 Gbps

Superior signal integrity at 28 Gbps and beyond

introspect

### Pin Electronic Design – Shmoo Capability

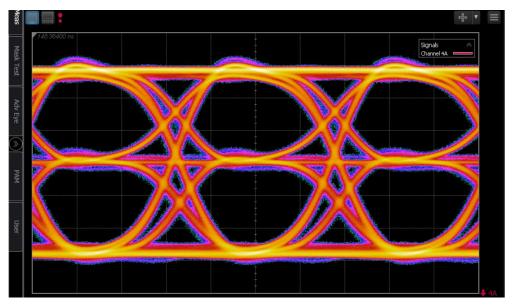

#### **DUT DQ Read at 28 Gbps** 600 400 200 Voltage (mV) 0 -200 -400-600 -2060 80 -400 20 40 Phase Delay (ps)

Receivers act as a window comparator to perform parallel PAM3 eye diagram measurement

#### All I/O Work as a Bus – 72 I/O per Package

### Pattern Handling Architecture

- HBM memory is used behind all pins in order to sustain bandwidth

- 2.88 Tbps of available test vector bandwidth

- Option for hardware-based or software-based scrambling, PAM3 encoding, and mapping

- Instruction sequencer includes "hold" and "idle" patterns

#### Software Architecture

#### $\sim$ DDR

#### 111 ŤĪ⊕

$(\bigcirc$

- +++ DramPhyParams 🛹 LpDramController

- +<mark>+</mark>+ LpDramParams

🛷 DramController

+++ DramParams

- +++ LpPhyParams

- +++ F

- RcdController

- +++ RcdParams

- AdimmController

- +++ GddrParams

- +++ GddrPhyParams

- CommandPa...

#### Components

#### 🧞 gddrChannelLabeling1

- 📌 gddrController1 +++ gddrParams1

- +++ gddrPhyParams1

- pam3Protocol

| PhyParams |

|-----------|

|-----------|

- 📌 GddrController

- ₀₁₀₀ DdrDataCapture

- E DdrDramCommand...

memBusesUnderTest ABCD  $\checkmark$ phyParams gddrPhyParams1  $\checkmark$ gddrParams gddrParams1 rxChannelLabeling  $\checkmark$ gddrChannelLabeling1 txChannelLabeling gddrChannelLabeling1 calibrateZq  $\checkmark$ True trainingDataCaPhase auto caPhaseTrainingNumStepsPerUi 32 trainingDataCaVref auto  $\sim$ caVrefTrainingStepSize 1 trainingDataReadVref  $\checkmark$ auto trainingDataReadPam3EyeOffset auto  $\checkmark$ trainingDataReadPhase  $\sim$ auto

1234

gddrController1

trainingDataFolderPath

deviceSerialNum

÷.

Virtual Memory Controller: automatically initialize and train the interfaces

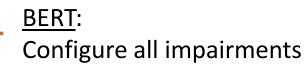

### PHY Characterization – Transmitter Interfaces

- Clock to data skew measurement

- RCK to DQ

- BERT measurements on clock and data

- Long duration error rate tests

- Eye diagrams

- Jitter measurements

- Slew rate measurements

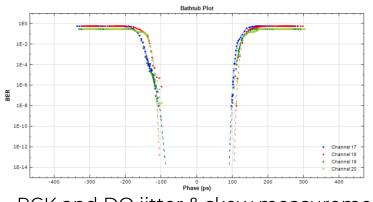

RCK and DQ jitter & skew measurement

RCK and DQ waveform measurement

#### PHY Characterization – Receiver Interfaces

- Measure horizontal and vertical eye opening at receiver while applying different stressors

- Timing & jitter sensitivity clock to data

- Voltage sensitivity

- Stressed eye

Introspeci

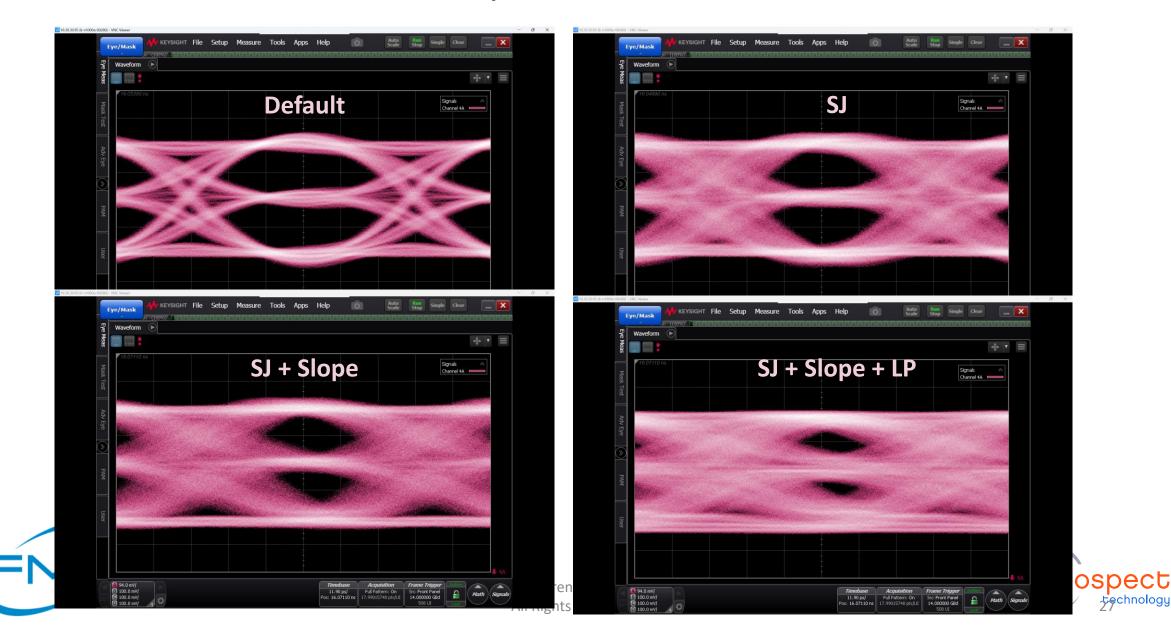

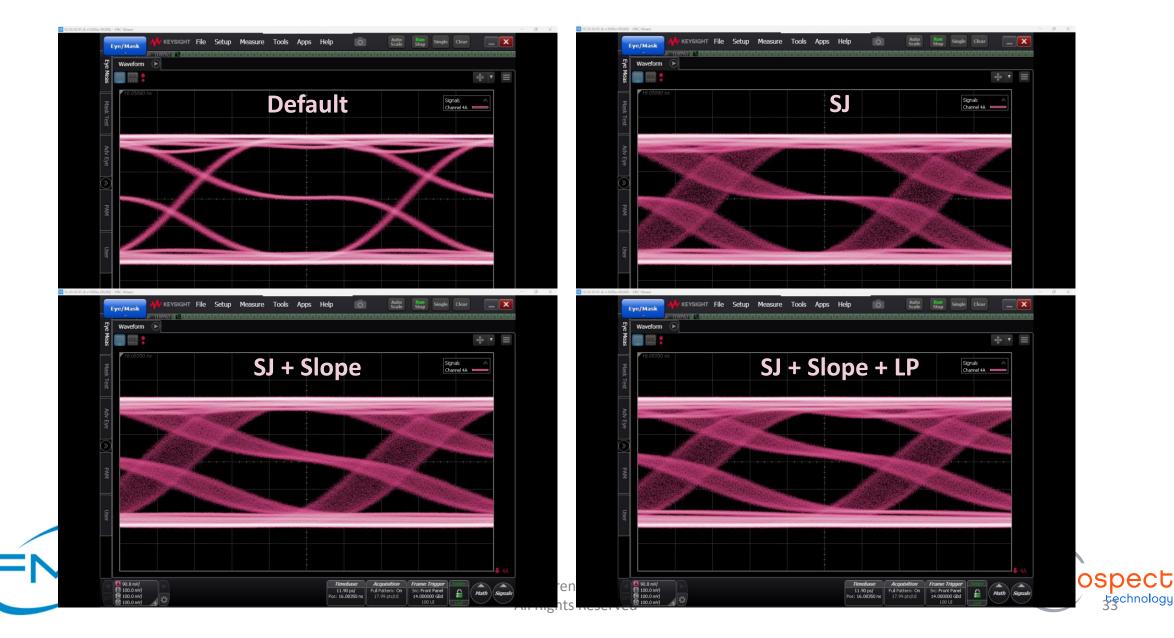

#### **Receiver Stressed Eye Generation**

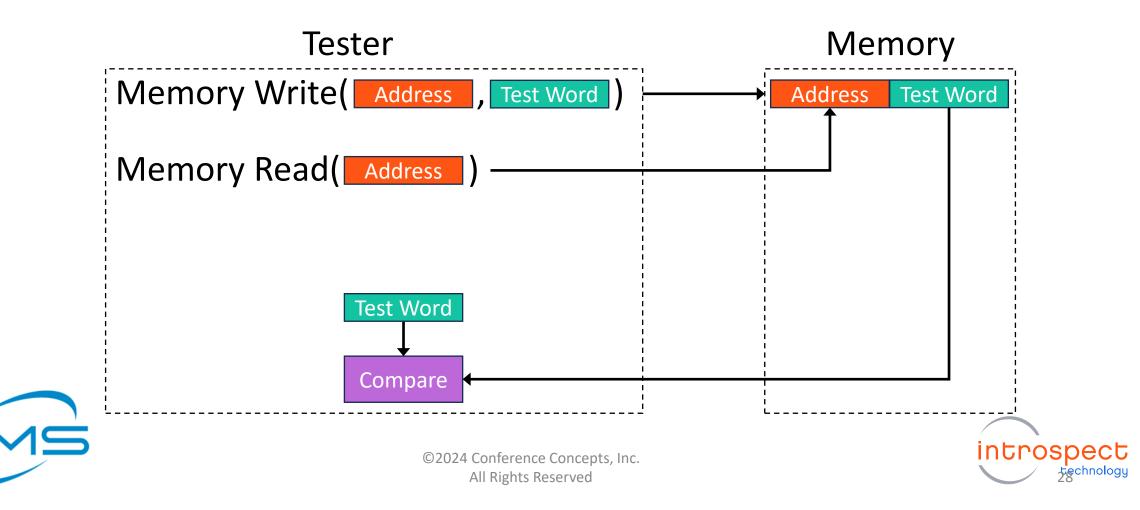

#### Memory Stress Test Pattern Scheduling

- Write-read-compare at each memory location

- Data Pattern = User-configurable Test Word

### Summary

- The <u>high-speed</u>, <u>burst-mode</u>, <u>single-ended</u>, <u>bidirectional</u>, <u>PAM3</u> signaling in GDDR7 all present significant electrical design and validation challenges

- The multiple <u>training modes</u> in GDDR7 also present design validation and stress testing challenges

- We have presented the design of an ATE on Bench solution for testing GDDR7 memories

- Acts like a high-performance BERT for electrical characterization

- Acts like a high-speed memory ATE for functional memory testing

#### Thank You!

Visit Us at Booth #851 https://introspect.ca

## Backup

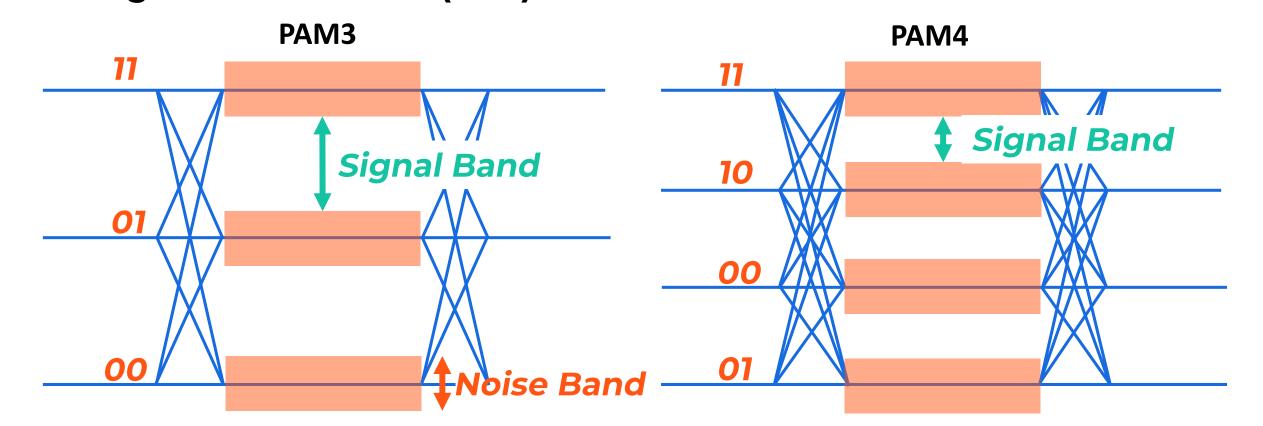

#### Why PAM3 and not PAM4? Signal to noise ratio (SNR) is much better in PAM3

For the same noise level, the PAM3 signal eye is much larger

#### Stressed-Eye Generation With Simple Pattern

#### Progressively Degraded PAM3 Waveforms

### Agenda

- Overview of GDDR7

- Goals of the ATE on Bench Design

- Pin Electronic Design

- Transmitter Characterization

- Receiver Characterization

- Memory functional stress testing