How UCIe Reduces the Barrier to Entry in Chiplet Design

UCIC-102-1: UCIe Technology Opportunities and Benefits: FMS 2024

Mayank Bhatnagar, Product Marketing Director, Cadence August 6, 2024

cadence

#### Agenda

Why chiplet-based designs are the future

System-in-package designs with and without a standard chiplet interface

Business case for increasingly expensive custom silicon

How chiplet ecosystem lowers barrier to entry

Comparison of various interface standards

Outlook for adoption of standards

## Why Chiplets?

#### Reticle size and yield issue

Pick right combination of nodes (optimize transistor cost)

Take advantage of package technology improvements

Modular and scalable design

Optimize for performance, power, and cost

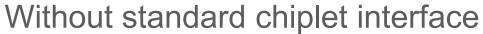

#### **Pre-Standardization Era**

Graphics Accelerator I/O Processor Analog

All chiplets designed in-house/same project

Need to design custom interface for each process

Design of non-differentiating chiplets takes resources

Quality limited by the availability of expertise in-house

Significant investment of design power and time

## Post-Standardization Paradigm Shift

With a widely adopted standard chiplet interface

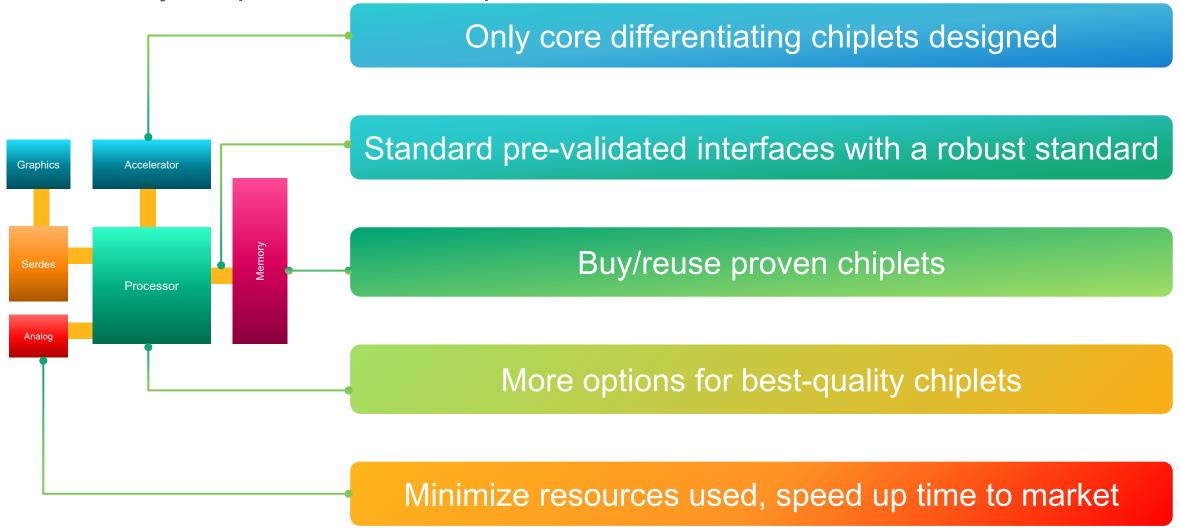

# Rising Cost of Large Designs

Source: IBS Global Semiconductor Industry Service Report: Design Activities and Strategic Implications, July 2018

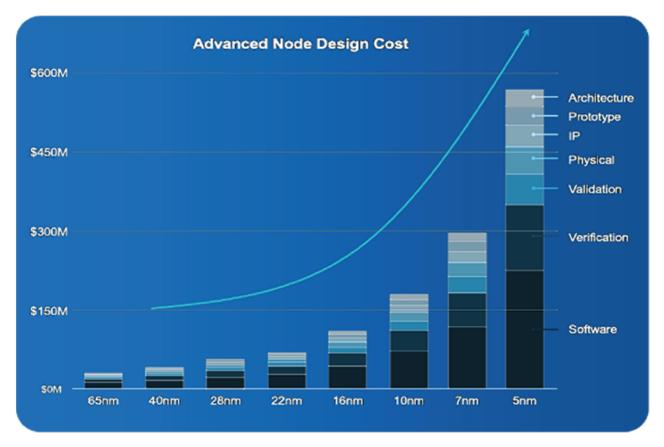

# Chiplet Ecosystem for Chiplet Designers: Use of Standard Interfaces

Internal (now) and external (long term) ecosystems

Standard

Custom core

Periphery

Build chiplet with highly customized core

Surround core with standard periphery, maximize serviceable market

Comprehensive standard for interface and to account for boundary effects

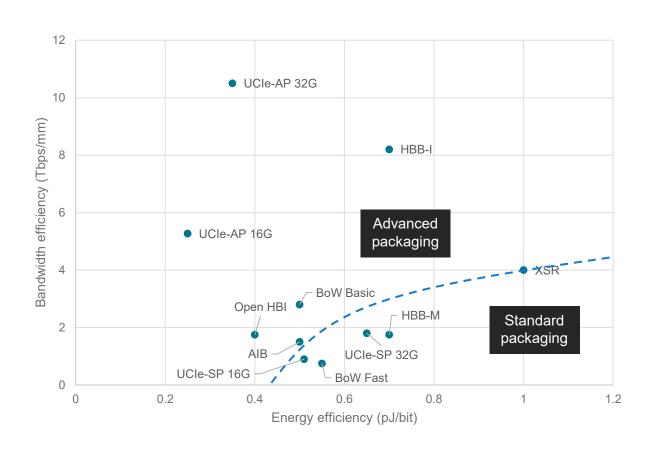

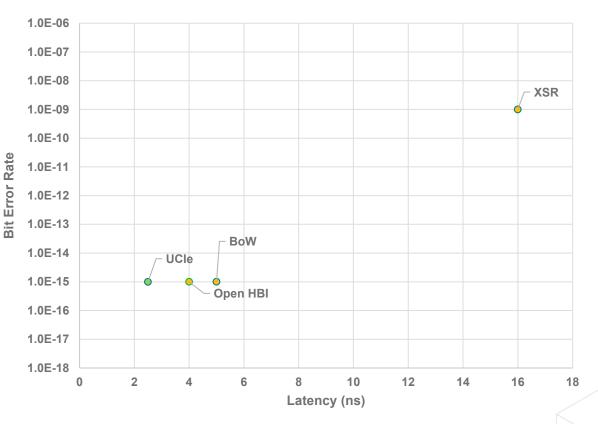

# Comparative Analysis of Chiplet Interconnect Standards Physical layer

Source: Cheolmin Park, "UCIe evolution and memory integration technology evolution for supercomputers", ISC-HPC 2023 Open Compute Project Open Domain-Specific Architecture comparison

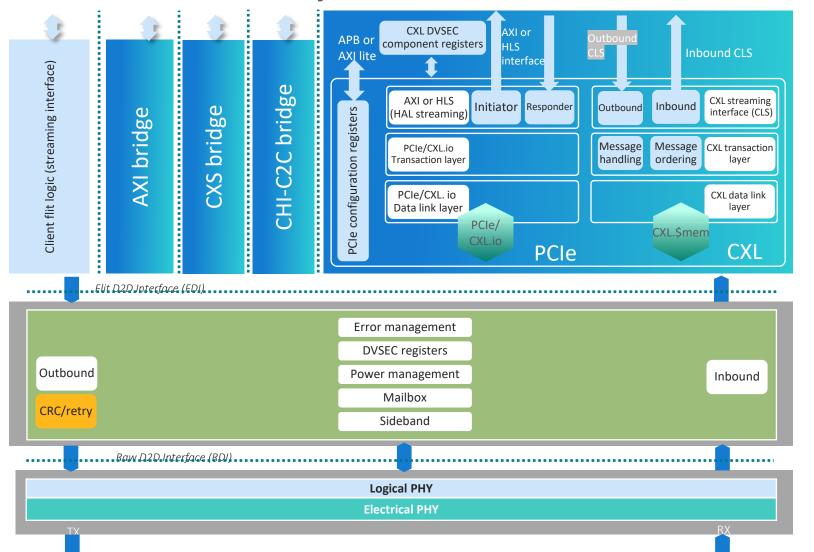

#### UCle – A Subsystem Solution

#### Protocol connectivity

Well-defined protocol layer

Streaming/bridges for disaggregation

PCIe and CXL for aggregation

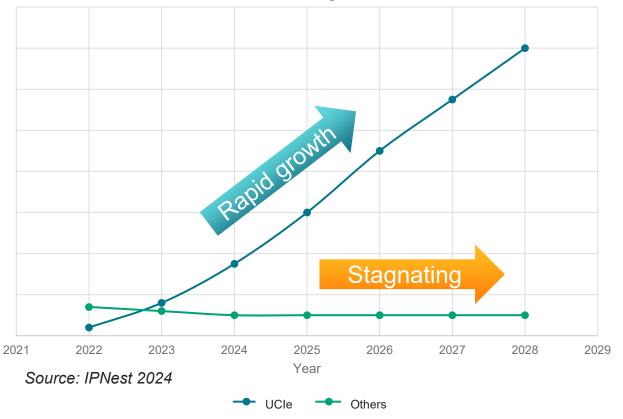

#### Outlook on Standard Adoptions

#### D2D IP design starts

D2D interconnects show signs of coalescing around UCle™

Interoperability will be a key factor in adoption

Rapid adoption of a common standard will unlock chiplet reuse

## Summary

Chiplets key to remaining profitable in semiconductor design

Standardization can yield significant benefits

Custom silicon needs chiplet ecosystem: internal and external

Standardization of periphery will make boutique chiplet design possible

UCle™ has the best technical metrics of all open standards

UCIe is gaining traction due to metrics and wide industry support

# cadence®

© 2024 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">https://www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or logo. All rights reserved worldwide. Cadence Design Systems, Inc. Accellera and Systems Inc. Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.