# High Performance Disaggregated Systems through UCIe Interconnects and Chiplets

## David Kulansky Director Product Marketing

Alphawave Semi © All Rights Reserved.

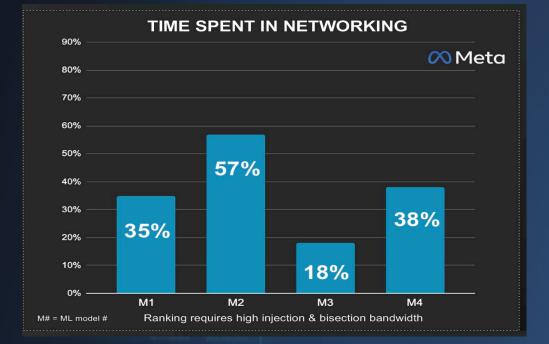

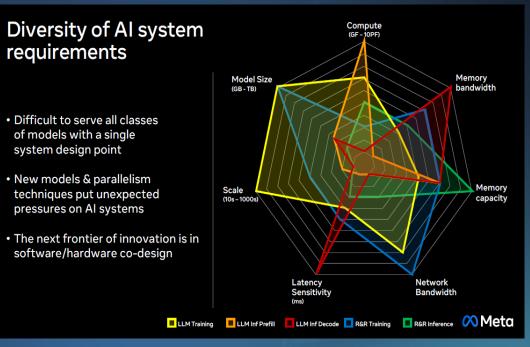

# Deploying AI at Scale - Data Centre Challenges

# Connectivity

**Custom Compute**

Source AI Summit : "Leading with Open" Meta

Al requires dedicated hardware with maximum communication bandwidth

Alphawave Semi © All Rights Reserved.

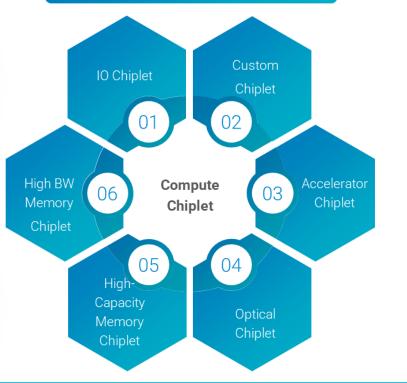

# Chiplets - Ushering a New Era of Semiconductors

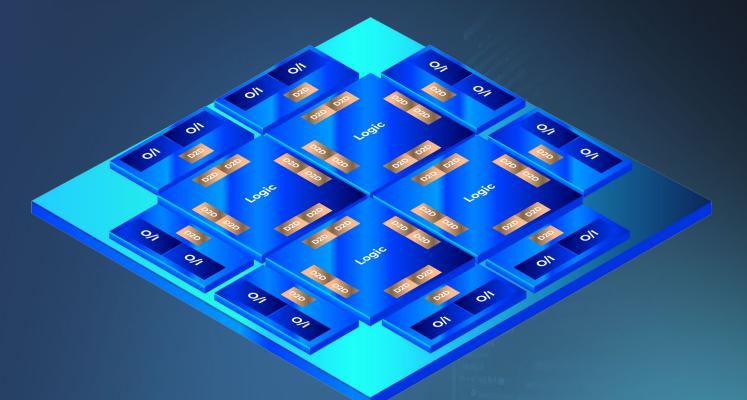

## The New Chiplet Design Paradigm

Chiplets rely on a fabric of dense high-speed die-to-die interconnect

Wide acceptance of the Universal Chiplet Interconnect Express<sup>1</sup> (UCIe<sup>™</sup>) standard in 2022 to accelerate and democratize the chiplet ecosystem

>

>

IC design and package optimizations are the future for advanced compute semiconductors

### DATACENTER SOC CHIPLETS

#### the Future of Memory and Storage

3

Alphawave Semi © All Rights Reserved.

# Chiplets: Accelerating the Adoption of Hardware Upgrades

- Reduced design time

- Reduced risk

- Composability

Alphawave Semi © All Rights Reserved.

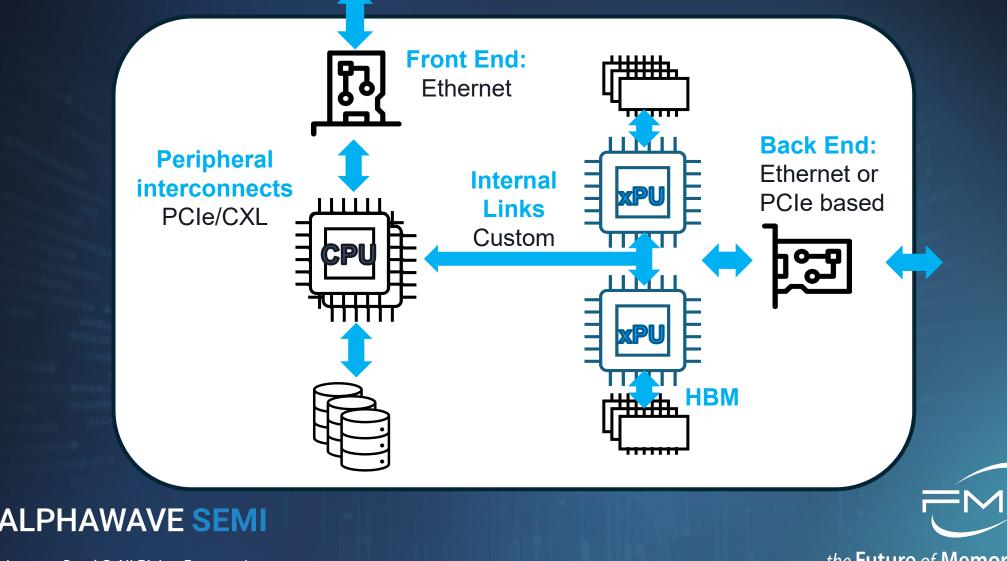

# Full AI Connectivity Suite Needed for Designing at Scale

Alphawave Semi © All Rights Reserved.

the Future of Memory and Storage

5

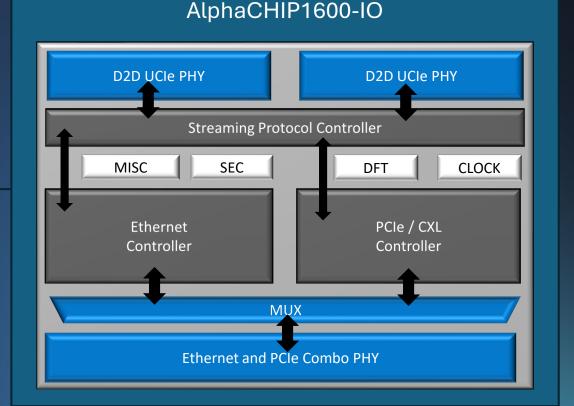

# Industry First, Multi-Protocol I/O Connectivity Chiplet

## AlphaCHIP1600-IO

- Reconfigurable Multi-Standard 112G SerDes I/O

- UCle Compliant ver1.1 D2D interconnect

- Integrated protocol controllers, security IP and UCIe PHY, and Controller IP that enables up to 1.6T of throughput at MR, XLR, and PCIe/CXL reach.

## Application

- Medium Reach Optical Driver Chiplet

- Extra Long Reach Ethernet Chiplet

- Combo PCIe/CXL/Ethernet Chiplet

- 1.6T high-speed I/O Chiplet

## the Future of Memory and Storage

6

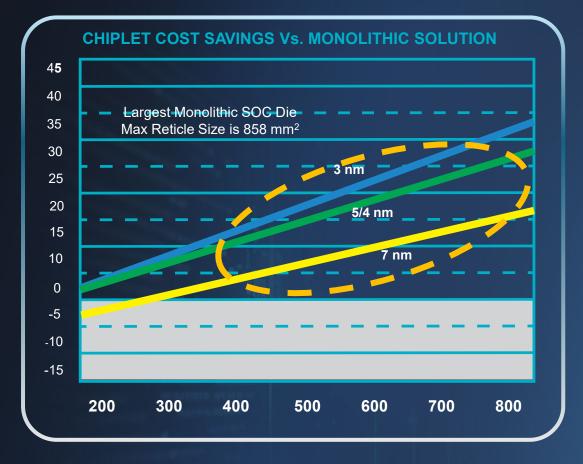

# Scaling Networking and Computing Barriers

| ©∽,<br>∏∏⊓ | Smaller Die<br>• Reduced die sizes, better yield                                                                                                                 | <b>Up to 40%</b><br>lower<br>die cost  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|            | Lower Non-Recurring<br>Engineering Cost<br>• Mix and match chiplets from different<br>nodes                                                                      | <b>Millions</b><br>saved in<br>NRE \$  |

| P          | <ul> <li>Lower Power</li> <li>Smaller die-to-die signal transfer (&lt; 0.3 pJ/lane)</li> <li>Ability to optimize voltages for each chiplet separately</li> </ul> | <b>25–50%</b><br>reduction in<br>power |

7

#### the Future of Memory and Storage

Alphawave Semi © All Rights Reserved.

## the Future of Memory and Storage

#### **Custom Silicon**

Spec-to-Silicon Capabilities Advanced 2.5D/3D Packaging Application Optimized IP Subsystems

Silicon IP

High Performance Connectivity IP

- PCIe/CXL

- Ethernet

- HBM/DDR

Chiplets

UCle ™ Enable

- I/O Chiplet

- Memory Chiplet

- Compute Chiplet

#### Connectivity Products

Industry Leading Electrical and Optical PAM4 and Coherent DSPs

# Thank You

Alphawave Semi © All Rights Reserved.

8