# Verification Challenges and Solutions for Multi-Die Systems

Prashant Dixit

Senior Engineering Manager

Siemens EDA

# Agenda

| Typical Functional Verification Solution                             |

|----------------------------------------------------------------------|

| Challenges                                                           |

| Verification IP                                                      |

| Verification Workflow                                                |

| Automatic testbench generation                                       |

| Verification Plan and Stimuli  Compliance Test Suite  SIG compliance |

| Verification IQ: Regression and coverage analysis                    |

| Protocol Checks                                                      |

| Debug: Trackers and Protocol Aware Debug                             |

| Summary                                                              |

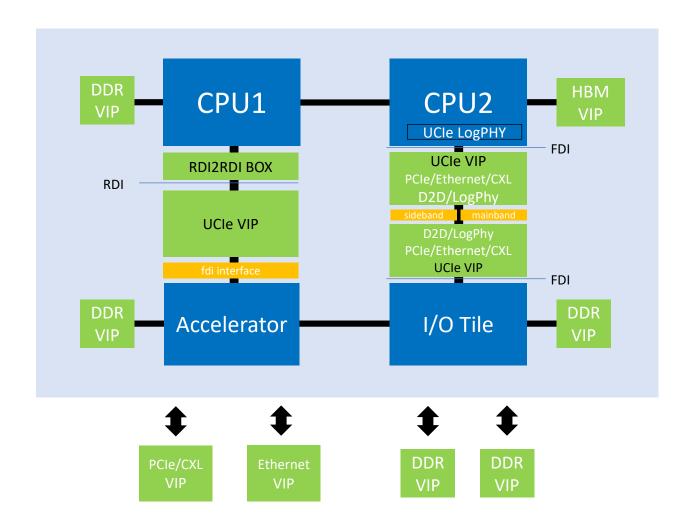

#### Multi-die SoC

#### Typical Functional Verification Solution

# Challenges

| Transition from block-level to system-level verification                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Update in the functionality, newer versions of products – changing the protocol layer                                                                                                                                                |

| Usability  ☐ useful APIs to achieve the desired scenarios ☐ common use cases to corner cases                                                                                                                                         |

| Controllability  ☐ traffic flowing from top layer to pin interface ☐ error injection testing ☐ Bypass initialization at each layer and each state of LTSM ☐ Blocking and non-blocking mode of txn ☐ Txn monitoring and scoreboarding |

| System-level analysis like bandwidth, throughput measurement, benchmarking                                                                                                                                                           |

| UVM Register Adapter Layer with model                                                                                                                                                                                                |

| Simulation to emulation and even prototyping scope                                                                                                                                                                                   |

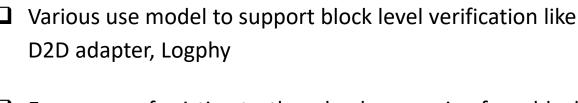

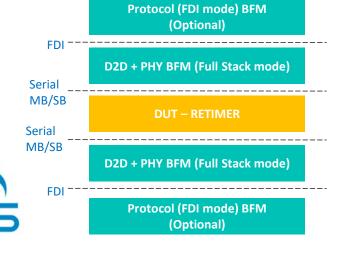

#### Block to subsystem to multi-die

- ☐ Easy reuse of existing testbench when moving from block-level to subsystem and multi-die environments

- ☐ Utilizing the existing infrastructure of block level in subsystem and multi-die level verification environment

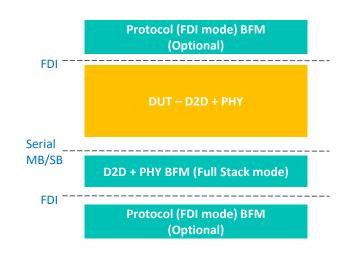

#### Common custom adapter layer

- Seamless integration of various protocol layer like PCIe, CXL or streaming protocols like AXI, CHI etc. with or without CXS/C2C

- ☐ PCIe/CXL-UCIe

- ☐ CHI-CXL-CXS-UCIe

- ☐ CHI-C2C-UCle

- ☐ AXI-C2C-UCle

- Easy migration of one to other using common adapter and adaptable higher layer stimulus using common APIs with no changes.

- ☐ Enables the reuse of various test related infrastructures (like regression suite, compliance test suites) of respective protocol layers over the UCle using the set of common APIs.

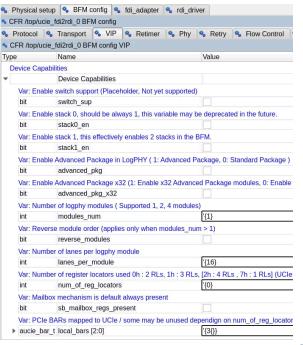

#### Usability: Ease of Use

- ☐ Only two data classes : Flit and Sideband packet

- ☐ Randomize flits, sideband packet with built in constraints

- ☐ Total and direct control on each field

- ☐ BFMs D2D handles sequence and CRC generation

- ☐ Built-in APIs for various operations

- ☐ Dynamic BFM behaviour variations

- ☐ Sending desired flits and sideband packets

- ☐ Entry/Exit APIs for cold reset

- ☐ Entry/Exit APIs for all LSM states

#### Controllability: Full Control

- ☐ Comprehensive callbacks to control the traffic flowing through various layers and components which enables

- scoreboarding

- performance monitoring

- error injection

- ☐ User traffic injection

- ☐ Built-in APIs for various operations

- ☐ LTSM transition

- pause/stall LTSM

- ☐ timeout scenarios

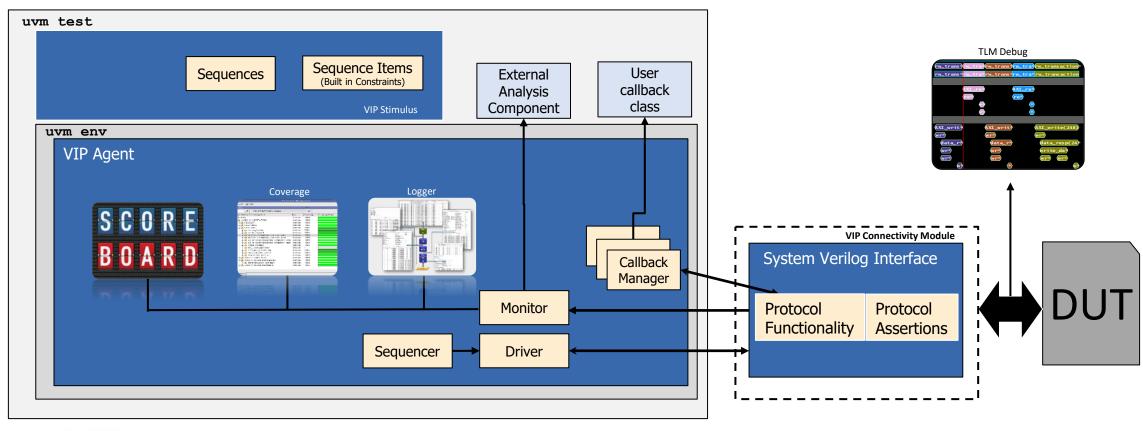

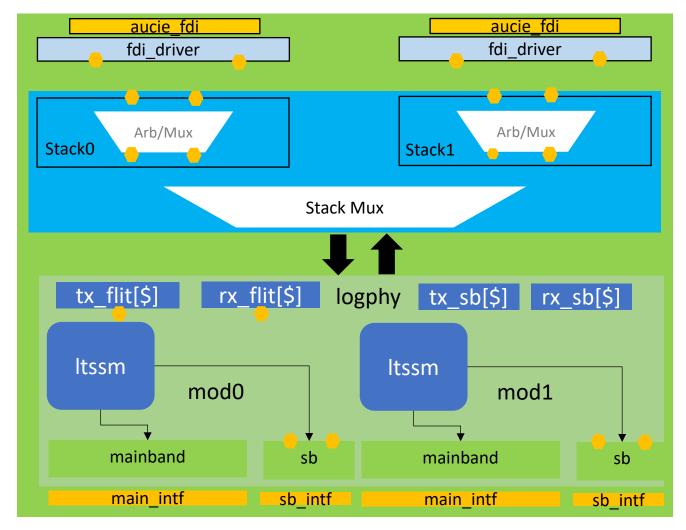

#### Verification IP

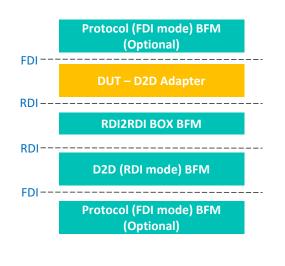

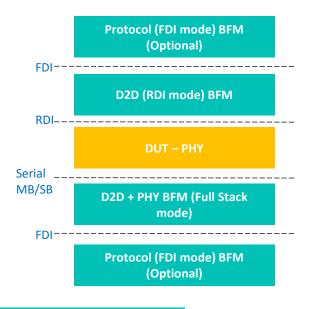

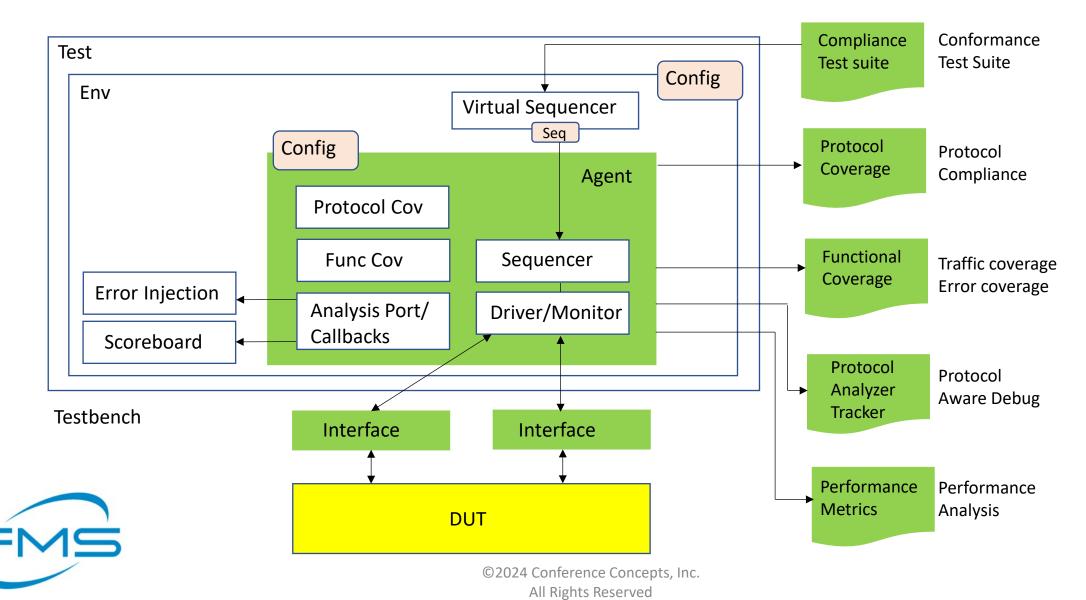

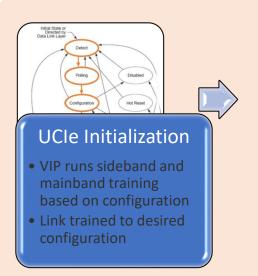

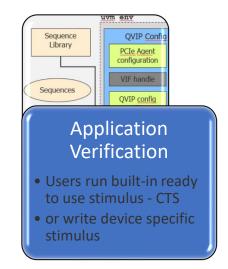

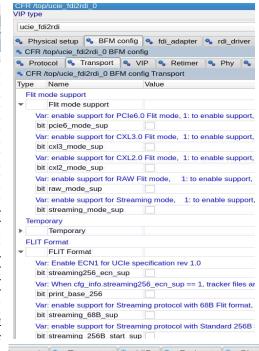

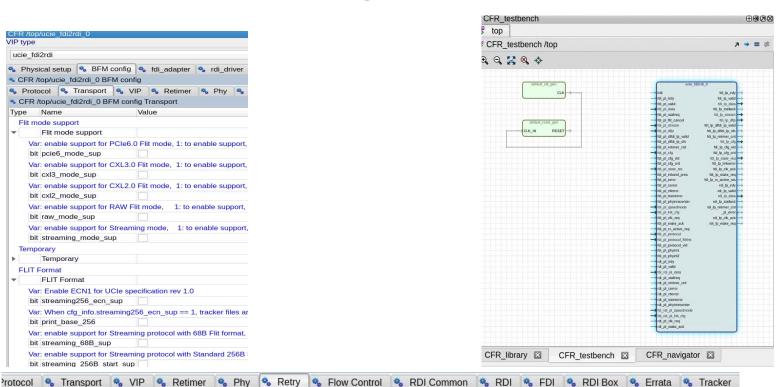

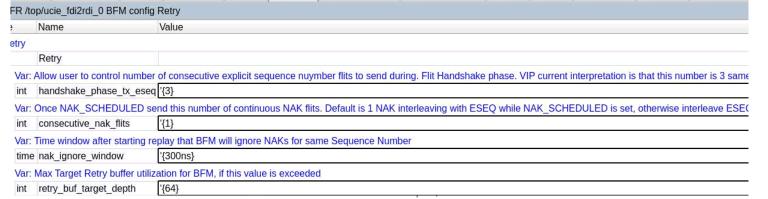

#### Verification Workflow

Getting Started possible in hours

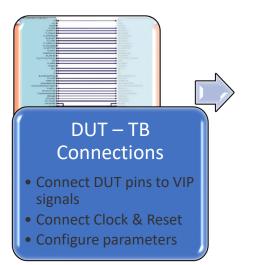

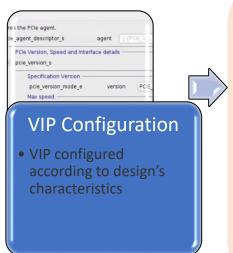

#### Automatic UVM testbench generation

#### Verification Plan with Stimuli

- ☐ Compliance Test Suite

- ☐ Exhaustive and ready to use test suite

- ☐ Covers all layers : Protocol, D2D adapter, logphy

- ☐ Covers all interfaces : FDI, RDI, mainband, sideband

- ☐ Config Space, LTSSM, sideband packets, retry, parity, parameter exchange

- ☐ Multi-module, multi-protocol

- ☐ Power Management

- ☐ Error injection scenarios for various errors

- ☐ Various resets

- ☐ Started on Security IDE, TDISP, SPDM/CMA, DOE, KM

- ☐ GUI based tool (VIQ) to enable feature/layer wise selection and run stimuli

#### Stimuli

- ☐ SIG compliance suite

- ☐ As per UCle specs

- ☐ PCle compliance

- ☐ CXL compliance

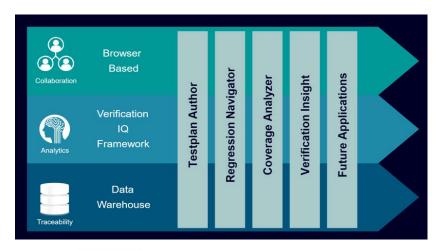

### Verification IQ (VIQ)

#### One tool to rule them all !!

- ☐ Unified support of multiple tools

- ☐ Collaborative tool with Analytical Navigation and Smart Visualization

- ☐ Test selection as per DUT feature support

- ☐ AI/ML based debug

- ☐ Smart Regressions

- ☐ Failure Predictors

- ☐ Smoke test predictors

- ☐ Accelerate Coverage Hole Debug

#### VIQ – Test Selection & analysis

| #            | Section                                          | Coverage % |

|--------------|--------------------------------------------------|------------|

| - 1          | Parity                                           | 100.00%    |

| <b>▶</b> 1.1 | aucie_uvm_err_inject_parity_seq                  | 100.00%    |

| ▶ 1.2        | aucie_uvm_enable_parity_seq                      | 100.00%    |

| 2            | Sideband                                         | 95.00%     |

|              | Parameter Exchange                               | 83.33%     |

| 4            | Retry                                            | 100.00%    |

| ▶ 4.1        | aucie_uvm_rand_flit_replay_seq                   | 100.00%    |

| ▶ 4.2        | aucie_uvm_ack_nak_ignore_seq                     | 100.00%    |

| ▶ 4.3        | aucie_uvm_nak_rule0_seq                          | 100.00%    |

| ▶ 4.4        | aucie_uvm_nak_rule2_seq                          | 100.00%    |

| ▶ 4.5        | aucie_uvm_seq_num0_acknak_seq                    | 100.00%    |

| ▶ 4.6        | aucie_uvm_nop_nak_timing_seq                     | 100.00%    |

| ▶ 4.7        | aucie_uvm_retimer_stall_seq                      | 100.00%    |

| 5            | LTSSM                                            | 98.00%     |

| ▶ 5.1        | SBINIT                                           | 100.00%    |

| ▶ 5.2        | MBINIT                                           | 100.00%    |

| ▶ 5.3        | MBTRAIN                                          | 100.00%    |

| ▼ 5.4        | PHYRETRAIN                                       | 88.00%     |

| ▶ 5.4.1      | aucie_uvm_adapter_init_phy_retrain_seq           | 80.00%     |

| ▶ 5.4.2      | aucie_uvm_config_retrain_seq                     | 100.00%    |

| ▶ 5.4.3      | aucie_uvm_multi_config_speed_change_seq          | 100.00%    |

| ▶ 5.4.4      | aucie_uvm_phy_init_phy_retrain_seq               | 80.00%     |

| ▶ 5.4.5      | aucie_uvm_phy_die_init_phy_retrain_seq           | 80.00%     |

| ▶ 5.5        | PM Flow                                          | 100.00%    |

| ▶ 5.6        | Miscellaneous                                    | 100.00%    |

| 6            | Config Space                                     | 100.00%    |

| ▼ 6.1        | UCIe Link DVSEC                                  | 100.00%    |

| ▶ 6.1.1      | aucie_uvm_check_ro_reg_dvsec_seq                 | 100.00%    |

| ▶ 6.1.2      | aucie_uvm_dvsec_default_reg_values_seq           | 100.00%    |

| ▶ 6.1.3      | aucie_uvm_dvsec_rsvd_chk_seq                     | 100.00%    |

| ▶ 6.1.4      | aucie_uvm_dvsec_cap_desc_chk_seq                 | 100.00%    |

|              | aucie_uvm_dvsec_link_cap_chk_seq                 | 100.00%    |

| ▶ 6.1.6      | aucie_uvm_dvsec_random_wr_rd_seq                 | 100.00%    |

| ▶ 6.1.7      | aucie_uvm_cfg_sp_raw_mode_and_adv_pkt_enable_seq | 100.00%    |

| ▶ 6.1.8      | aucie_uvm_link_status_change_seq                 | 100.00%    |

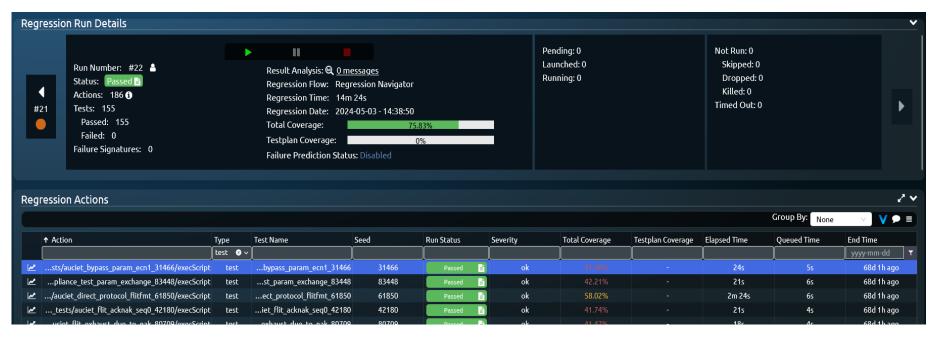

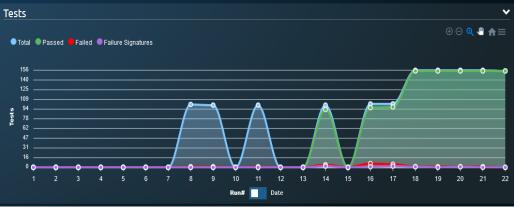

#### VIQ – Regression Analysis

- ☐ Quick summary for regression run

- ☐ Result analysis and incremental run

- ☐ Failure signature detection

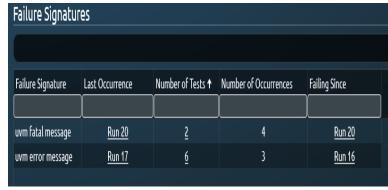

### VIQ – Coverage Analysis

- ☐ Hole analysis

- ☐ Heatmaps

- ☐ Bin distribution

#### **Protocol Checks**

- ☐ Exhaustive set of protocol checks (~500)

- ☐ FDI, RDI, Logphy, Config Space

- Parameter Negotiation

- □ PCIe, CXL and AXI checks (~3000)

- ☐ Coverage of protocol checks

- make sures that all the protocol scenarios has been exercised without violation

```

AUCIE ERROR 1US PM HANDSHAKE,

AUCIE ERROR FLIT CRC,

AUCIE ERROR RX SEQ NUMO

AUCIE ERROR RX INVALID SEO NUM,

AUCIE_ERROR_REPLAY_TIMEOUT,

AUCIE REPLAY TIMEOUT,

AUCIE_ESEQ_HANDSHAKE_TIMEOUT,

AUCIE ERROR UR DATA 1,

AUCIE ERROR DVSEC OFFSET,

AUCIE ERROR NON IDLE EXPLICIT SEQ RX,

AUCIE ERROR BAD SEQ NUMBER,

AUCIE ERROR FLIT CRC WAIT NAK,

AUCIE ERROR INVALID SEQ NUM WAIT NAK,

AUCIE SCHEDULE REPLAY,

AUCIE ERROR DUPLICATE SEQ,

AUCIE NAK SCHEDULE 1,

AUCIE ACK SCHEDULE 1,

AUCIE FLIT DISCARD 0,

AUCIE_ERROR_NAK_RECEIVED

AUCIE ERROR INVALID STACK ID,

AUCIE ERROR RX PARITY,

AUCIE PARAM EXCHANGE TIMEOUT,

AUCIE ERROR CP PARITY,

AUCIE_ERROR_DP_PARITY,

AUCIE ERROR SRCID,

AUCIE_ERROR_DSTID,

AUCIE_ERROR_SRC_DST_ID1,

AUCIE ERROR SRC DST ID2,

AUCIE ERROR SRC DST ID3,

AUCIE ERROR SRC DST ID4,

AUCIE_ERROR_VALID_SIGNAL,

AUCIE_LTSSM_TIMEOUT_ERROR,

AUCIE_LFSR_PATTERN_CHECK,

AUCIE_WARN_ERROR_READ_CFGSB,

AUCIE ERROR NO EZE CREDITS,

AUCIE ERROR EZE CREDITS EXEEDED,

AUCIE ERROR E2E INVALID MSG INFO,

AUCIE INVALID SB ADDR RL,

AUCIE ERR CONSECUTIVE ACKNAK,

AUCIE ERROR SB OPCODE INVALID,

AUCIE ERROR SB FIELD INVALID,

AUCIE_ERROR_SB_MSG_INFO_INVALID,

AUCIE_ERROR_FLIT_FIELD_ERR,

AUCIE ERROR MBINIT PARAMS,

AUCIE ERROR FDI RDI SB PAYLOAD SIZE,

AUCIE ERROR CREDIT MISMATCH RDI,

AUCIE ERROR CREDIT MISMATCH FDI,

AUCIE ERROR CREDIT UNDERFLOW RDI,

AUCIE ERROR CREDIT UNDERFLOW FDI,

AUCIE ERROR CREDIT OVERFLOW RDI,

AUCIE ERROR CREDIT OVERFLOW FDI,

AUCIE ERROR NO RESERVED SDID FDI,

AUCIE ERROR RSVD BE REQ,

AUCIE ERROR RSVD_BE_CPL,

QUCIE ERROR NOP NAK WAIT,

AUCIE ERROR INVALID LATENCY AVG.

AUCIE ERROR INVALID LATENCY MED,

AUCIE ERROR INVALID LATENCY HIGH,

AUCIE ERROR INVALID LATENCY LOW,

AUCIE ERROR INVALID PERFORMANCE TX AVG,

AUCIE ERROR INVALID PERFORMANCE TX MED,

AUCIE_ERROR_INVALID_PERFORMANCE_TX_HIGH,

AUCIE ERROR INVALID PERFORMANCE TX LOW,

AUCIE_ERROR_INVALID_PERFORMANCE_TX_CALCULATED,

AUCIE_ERROR_INVALID_PERFORMANCE_RX_AVG,

AUCIE ERROR INVALID PERFORMANCE RX MED, AUCIE ERROR INVALID PERFORMANCE RX HIGH,

AUCIE ERROR INVALID PERFORMANCE RX LOW,

AUCIE_ERROR_INVALID_PERFORMANCE_RX_CALCULATED,

AUCIE ERROR STACK ROUND ROBIN,

AUCIE RETIMER STALL TIMEOUT,

AUCIE PARAM EXCHANGE FAIL,

AUCIE FDI RETRAIN ERROR.

AUCIE_ERROR_RUNTIME_RECALIBRATION,

AUCIE ERROR PCIE CAP EN,

```

#### Debug Tools

- ☐ Debug Messages

- ☐ Trackers and transcript

- ☐ Protocol Aware Debug

#### Debug messages

```

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] aucie module::exit cold reset()

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting logphy

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting module : 3

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] mode = AUCIE MODULE tx rx

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] aucie module

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting sb deserializer

uvm test top.env0.bfml.bfml log [AUCIE INF] Starting module : 2

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] mode = AUCIE MODULE tx rx

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] aucie module

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting sb deserializer

uvm test top.env0.bfml.bfml log [AUCIE INF] Starting module : 1

uvm test top.env0.bfml.bfml log [AUCIE INF] mode = AUCIE MODULE tx rx

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] aucie module

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting sb deserializer

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting module : 0

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] mode = AUCIE MODULE tx rx

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] aucie module

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Starting sb deserializer

```

```

uvm test top.env0.bfm2.bfm2 log [AUCIE INF] AVERY: ECN1: Advertising additional bits in {FinCap.Adapter}

uvm test top.env0.bfm2.bfm2 log [AUCIE INF]

cfg info.streaming 68B sup:

uvm test top.env0.bfm2.bfm2 log [AUCIE INF]

cfg info.streaming 256B end sup:

uvm test top.env0.bfm2.bfm2 log [AUCIE INF]

cfg info.streaming 256B start sup:

uvm test top.env0.bfm2.bfm2 log [AUCIE INF]

cfg info.streaming 256B lom w ob sup:

uvm test top.env0.bfm2.bfm2 log [AUCIE INF]

cfg info.streaming 256B lom no ob sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] AVERY: ECN1: Advertising additional bits in {FinCap.Adapter}

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

cfg info.streaming 68B sup:

uvm_test_top.env0.bfm1.bfm1_log [AUCIE_INF]

cfg_info.streaming_256B_end_sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

cfg info.streaming 256B start sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

cfg info.streaming 256B lom w ob sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

cfg info.streaming 256B lom no ob sup: 1

uvm test top.env0.bfm1.bfm1 log [AUCIE INF] Received {AUCIE SIDE MSG AdvCap Adapter}

uvm test top.env0.bfml.bfml log [AUCIE INF] Received {AUCIE SIDE MSG AdvCap Adapter}

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.retimer en:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.cxl lat opt fmt6 sup:

advCap.cxl lat opt fmt5 sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.stack0 en:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.stack1 en:

advCap.multi protocol en:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.retry sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.streaming mode sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.pcie6 mode sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.cxl3 mode sup:

uvm_test_top.env0.bfm1.bfm1_log [AUCIE INF]

advCap.cxl2 mode sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.raw mode sup:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.UP:

uvm test top.env0.bfm1.bfm1 log [AUCIE INF]

advCap.DP:

```

```

uvm_test_top.env0.bfm1.bfm1_log [AUCIE_INF] FDI BRINGUP PROCESS ENDS

uvm_test_top.env0.bfm1.bfm1_log [AUCIE_INF] STARTING FDI BRINGUP PROCESS

bfm2"(mod0): LTSSM go to AUCIE_LTSSM_RESET

uvm_test_top.env0.bfm2.bfm2_log [AUCIE_INF] FDI BRINGUP PROCESS ENDS

uvm_test_top.env0.bfm2.bfm2_log [AUCIE_INF] STARTING FDI BRINGUP PROCESS

```

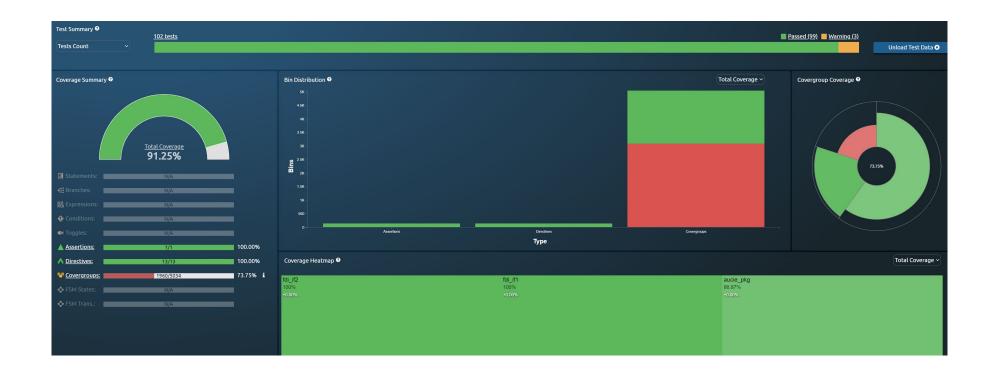

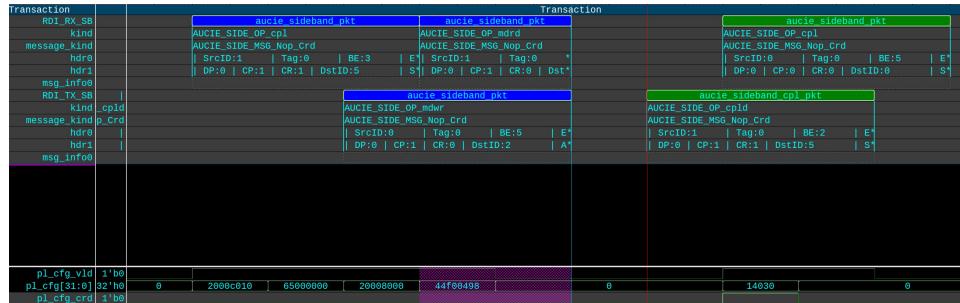

#### Debug using trackers

- Visualize transactions in "spec" formats

- Sideband Packets

- FLITs, etc.

- Multiple trackers for each layer

- FDI, RDI, D2D

- Logphy

- Correlated between layers and multi-protocol stacks (PCIe-UCIe), (CXL-UCIe), (AXI-UCIe) etc.

- conditional user annotations to pin-point transactions and bugs quickly

```

DP:1 | CP:0 | DstID:5 | MsgInfo:0

Data [63:32]: 00000000

[3] PCIe Flit Mode: 0

[4] Streaming: 1

Multi Protocol Enable: 0

[9] CXL LatOpt Fmt5: 0

[10] CXL LatOpt Fmt6: 0

[11] Retimer: 0

[20:12] Retimer Credits: 'd1024

[22] UP: 1

[23] 68B Flit Format: 0

[24] Standard 256B End Header Flit Format: 1

[25] Standard 256B Start Header Flit Format: 0

[26] Latency-Optimized 256B without Optional Bytes

[27] Latency-Optimized 256B with Optional Bytes

[28] Enhanced Multi Protocol Enable: 0

Stack 0 Maximum Bandwidth Limit: 0

```

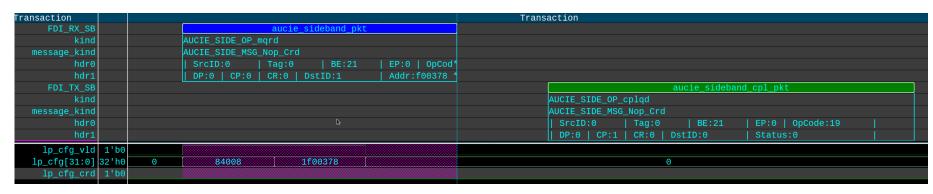

#### Protocol Aware Debug

## Protocol Aware Debug (contd..)

| Transaction         |                                         |                                   | Tr                           | ansaction                 |              |                                             |                            |                             |            |  |

|---------------------|-----------------------------------------|-----------------------------------|------------------------------|---------------------------|--------------|---------------------------------------------|----------------------------|-----------------------------|------------|--|

| RDI_TX_MB           | nop_flit                                |                                   | lp_data                      |                           |              | )                                           | lp_data                    |                             |            |  |

| kind                | AUCIE_FLIT_KIND_FMT3_PCIE               | AUCIE_FLIT_KIND_FMT3_PCIE         |                              | AUCIE_FLIT_KIND_FMT3_PCIE |              |                                             | AUCIE_FLIT_KIND_FMT3_PCIE  |                             |            |  |

| raw                 | 0                                       |                                   | Θ                            |                           |              |                                             | Θ                          |                             |            |  |

| f2                  | 0                                       |                                   | Θ                            |                           |              |                                             | Θ                          |                             |            |  |

| u                   | 1c0000000000000000000000000000000000000 | 6770db34eb50aa543c86ac35e4f8ca4b* |                              |                           | k            | 7d817390184efd896f2ca63ce207a951            |                            |                             |            |  |

| raw_bytes_0_        | 0                                       |                                   | 79                           |                           |              |                                             | 9                          |                             |            |  |

| raw_bytes_1_        | 0                                       |                                   | 6a                           |                           |              |                                             | 83                         |                             |            |  |

| raw_bytes_2_        | 0                                       | 52<br>38<br>e8                    |                              |                           | С            |                                             |                            |                             |            |  |

| raw_bytes_3_        | 0                                       |                                   |                              |                           |              | 83                                          |                            |                             |            |  |

| raw_bytes_4_        | 0                                       |                                   |                              |                           |              | 66                                          |                            |                             |            |  |

| raw_bytes_251_      | 0                                       |                                   | 0                            |                           |              |                                             | Θ                          |                             |            |  |

| raw_bytes_252_      | 0                                       |                                   | f1                           |                           |              |                                             | 6e                         |                             |            |  |

| raw_bytes_253_      | 0                                       | 89                                |                              |                           |              | 88<br>36<br>ca<br>AUCIE_FLIT_KIND_FMT3_PCIE |                            |                             |            |  |

| raw_bytes_254_      | 49                                      | 8f<br>49                          |                              |                           |              |                                             |                            |                             |            |  |

| raw_bytes_255_      | eb                                      |                                   |                              |                           |              |                                             |                            |                             |            |  |

| Flit_type           | AUCIE_FLIT_KIND_FMT3_PCIE               | AUCIE_FLIT_KIND_FMT3_PCIE         |                              |                           |              |                                             |                            |                             |            |  |

| Flit                | NOP                                     |                                   | Payload FLi                  | .t                        |              |                                             | Payload FL                 | it                          |            |  |

| ack_nak             | ACK                                     |                                   | ESEQ                         |                           |              |                                             | ACK                        |                             |            |  |

| seq_num             | c                                       |                                   | f                            |                           |              |                                             | d                          |                             |            |  |

| STACK               | 0                                       |                                   | 0                            |                           |              |                                             | 0                          |                             |            |  |

| lp_valid 1'b1       |                                         |                                   |                              |                           |              |                                             |                            |                             |            |  |

| pl_trdy 1'b1        |                                         |                                   |                              |                           |              |                                             |                            |                             |            |  |

| lp_data[63:0] 3817d | 0                                       | eb49000000                        | )* <mark>edaa45883e</mark> * | 156ca74302                | *6d85497aff* | 498f89f100                                  | 9* <mark>476de8e426</mark> | * <mark>65de3dc2d5</mark> * | 758cc4d861 |  |

| lp_data[63] 8'h75   | 0                                       | eb                                | ed                           | 1                         | 6d           | 49                                          | 47                         | 65                          | 75         |  |

| lp_data[62] 8'h8c   | 0                                       | 49                                | aa                           | 56                        | 85           | 8f                                          | 6d                         | de                          | 8c         |  |

| lp_data[61] 8'hc4   | 0                                       |                                   | 45                           | ca                        | 49           | 89                                          | e8                         | 3d                          | C4         |  |

| lp_data[60] 8'hd8   | 0                                       |                                   | 88                           | 74                        | 7a           | f1                                          | e4                         | c2                          | d8         |  |

| lp_data[59] 8'h61   | 0                                       |                                   | 3e                           | 30                        | ff           | 0                                           | 26                         | d5                          | 61         |  |

| lp data[58] 8'h24   | 0                                       |                                   | 91                           | 26                        | 65           | 0                                           | 8a                         | 1f                          | 24         |  |

#### Performance Measurement

- Performance summary log on Tx and Rx bus

- Configurable for a particular simulation window

#### TX PERFORMANCE SUMMARY

Performance TX AVG: 64032.080201 MB/s

Performance TX MED: 59733.333333 MB/s

Performance TX HIGH: 68266.666667 MB/s

Performance TX LOW: 59733.333333 MB/s

#### RX PERFORMANCE SUMMARY

Performance RX AVG: 63903.759398 MB/s

Performance RX MED: 68266.666667 MB/s

Performance RX HIGH: 68266.666667 MB/s

Performance RX LOW: 51200.000000 MB/s

#### Summary

- ☐ Automatic UVM-TB generation

- ☐ Compliance test suites (ready to use exhaustive stimulus)

- ☐ VIP controllability to hit corner case scenarios

- ☐ Usability for ease of use

- ☐ Debug tools

- ☐ Discussed features enabled our customers to verify the designs faster and achieve lesser time to market

#### Questions ??

Please visit booth # 1051 (Siemens) for more information