### Life Beyond Flash New Non-Volatile Memory Technologies

Bill Gervasi Principal Systems Architect bilge@Nantero.com

Santa Clara, CA August 2019

# Data processing is great

# Data processing is great

## **Until something goes**

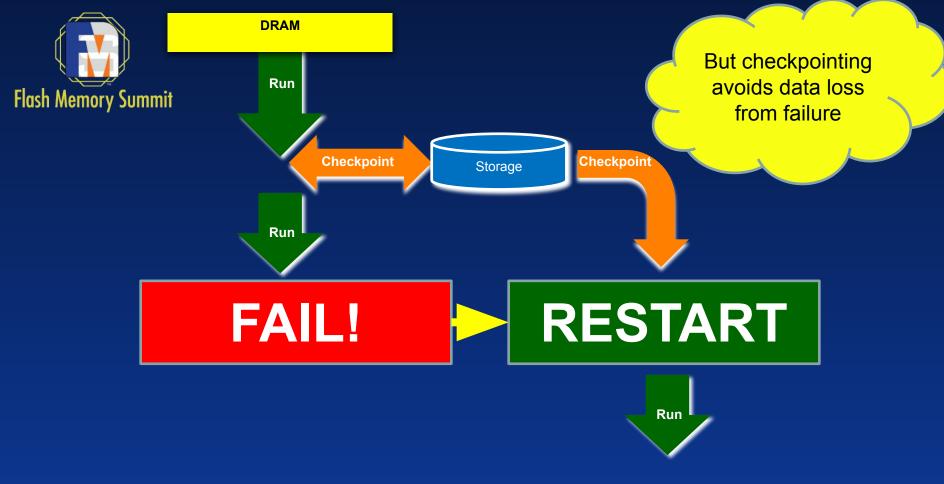

#### Checkpoint

🛗 November 12, 2015 🙎 Alexandr Omelchenko 🛸 Glossary

#### ★★★★★ [Total: 21 Average: 4.2/5]

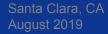

Checkpoint is a process that writes current in-memory dirty pages (modified pages) and transaction log records to physical disk. In SQL Server checkpoints are used to reduce the time required for recovery in the event of system failure. Checkpoint is regularly issued for each database. The following set of operations starts when checkpoint occurs:

- 1. Log records from log buffer (including the last log record) are written to the disk.

- All dirty data file pages (pages that have been modified since the last checkpoint or since they were read from disk) are written into the data file from the buffer cache.

- 3. Checkpoint LSN is recorded in the database boot page.

Santa Clara, CA August 2019

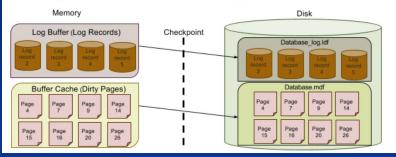

#### Checkpointing invented to compensate for volatile nature of main memory

# Save work in progress in case things crash

**Storage**

Memory

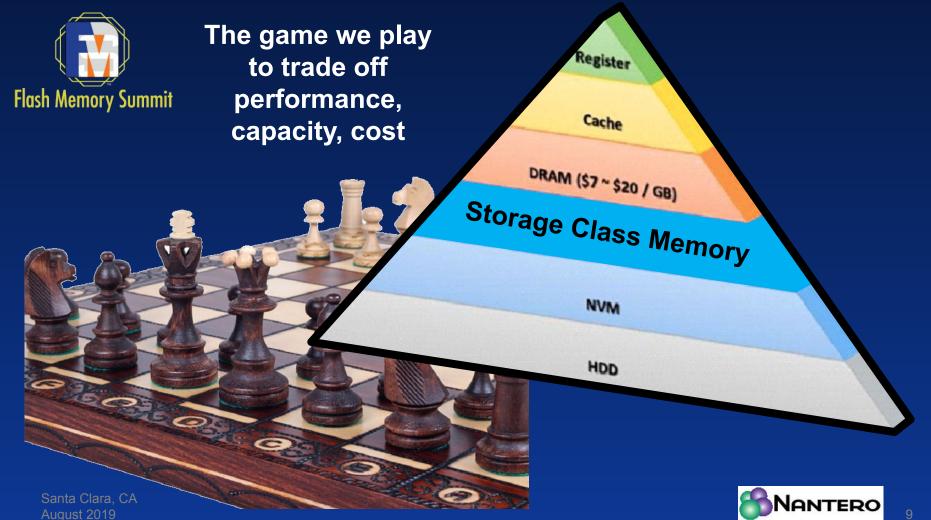

## Storage access time impacts transaction granularity

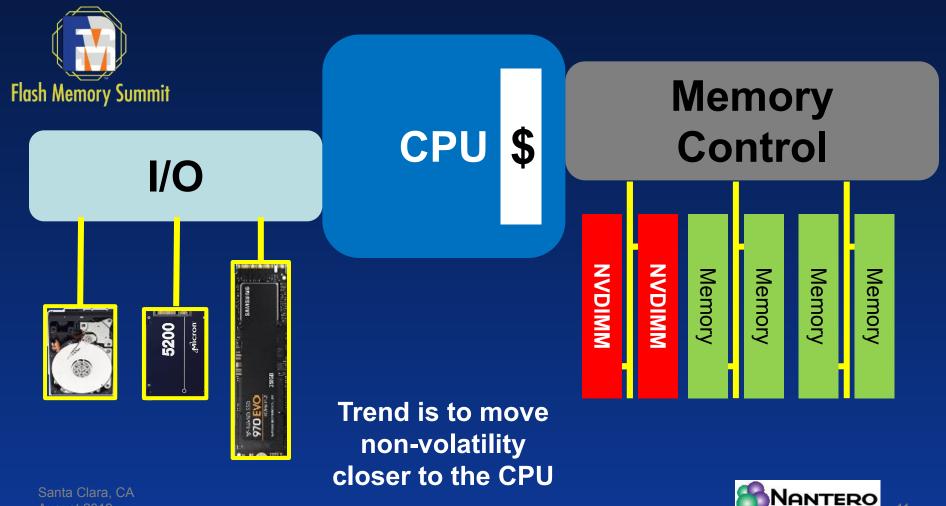

Data persistence is essential

CPU

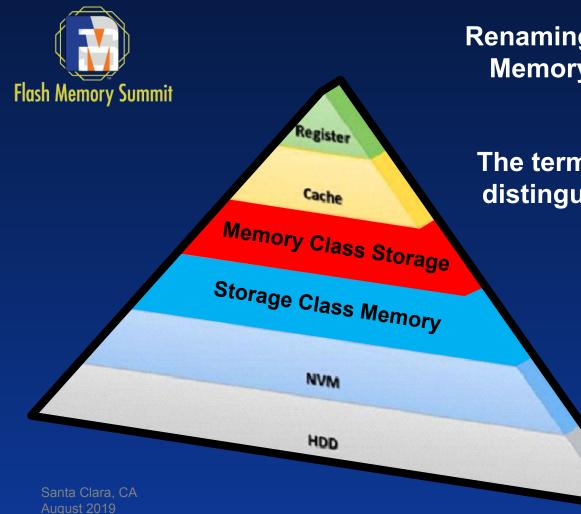

Renaming SCM as "Persistent Memory" missed the mark

The term "Memory Class Storage" distinguishes DRAM replacement technologies

> MCS & SCM are both persistent, just have very different performances

# HE HOLY GRAIL

Santa Clara, CA August 2019

Flash Memory

#### End to end....

# **Data Persistence**

#### ...but without giving up PERFORMANCE

## Memory Class Storage Checklist

Persistent

No compromise DRAM speed

Fully deterministic

No device wear out visible to the controller Interface protocol compliant, e.g., DDR5

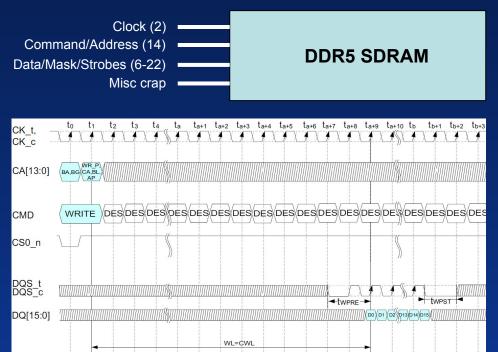

#### What exactly is DDR5, anyway?

#### Signaling protocol for CPU to DRAM

Tradeoff of performance versus pin count

Designed to "just meet" target speeds

Single-ended signals, differential clocks/strobes

Bi-directional data bus

Byte level data masking

Deterministic timing from command to data

ECC required on data

Multiplexed address/command signals

Some flexibility on data latencies

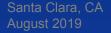

#### **DDR5 SDRAM Core Functions**

Activate Read Write Precharge Refresh Self Refresh

Fetches data from the array to sense amps

Reads data from sense amps

Writes data to sense amps

Restores data from sense amps to the array

Restores charge levels in the array

Keeps data valid while device is idle

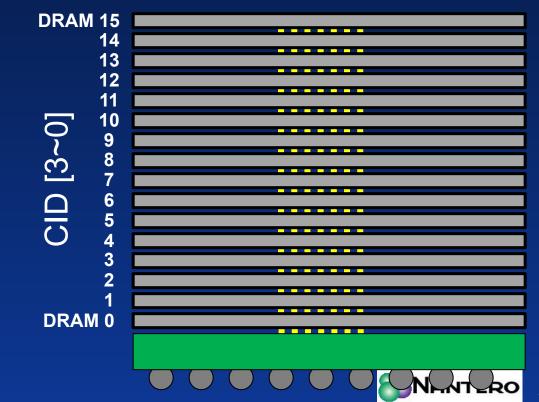

#### Chip ID

### Selects one DRAM die within a stack of die in a package

0

| Bank<br>Group<br>7 | 6 | 8 BANK GROUPS WITH 4 BANKS PER GROUP =<br>32 BANKS PER DRAM DIE<br>5 4 3 2 1 |   |   |   |   |        |  |  |  |  |

|--------------------|---|------------------------------------------------------------------------------|---|---|---|---|--------|--|--|--|--|

| BANK 3             | 3 | 3                                                                            | 3 | 3 | 3 | 3 | BANK 3 |  |  |  |  |

| BANK 2             | 2 | 2                                                                            | 2 | 2 | 2 | 2 | BANK 2 |  |  |  |  |

| BANK 1             | 1 | 1                                                                            | 1 | 1 | 1 | 1 | BANK 1 |  |  |  |  |

| BANK 0             | 0 | 0                                                                            | 0 | 0 | 0 | 0 | BANK 0 |  |  |  |  |

### COOLDS WITH A BANKS DED COOLD

|                                 | Table 9 — 3                     | 32 Gb Addressing | Table        |              |  |

|---------------------------------|---------------------------------|------------------|--------------|--------------|--|

|                                 | Configuration                   | 8 Gb x4          | 4 Gb x8      | 2 Gb x16     |  |

|                                 | BG Address                      | BG0~BG2          | BG0~BG2      | BG0~BG1      |  |

| Bank<br>Address                 | Bank Address in a BG            | BA0~BA1          | BA0~BA1      | BA0~BA1      |  |

| Address                         | # BG / # Banks per BG / # Banks | 8/4/32           | 8/4/32       | 4/4/16       |  |

|                                 | Row Address                     | R0~R16           | R0~R16       | R0~R16       |  |

| Column Address                  |                                 | C0~C10           | C0~C9        | C0~C9        |  |

|                                 | Page size                       | 1KB              | 1KB          | 2KB          |  |

| Chip IDs / Maximum Stack Height |                                 | CID0~3 / 16H     | CID0~3 / 16H | CID0~3 / 16H |  |

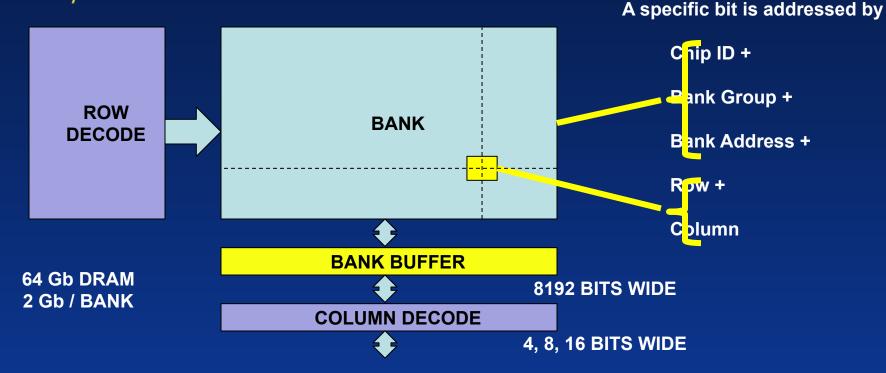

#### Table 10 — 64 Gb Addressing Table

|                 | Configuration                   | 16 Gb x4    | 8 Gb x8     | 4 Gb x16    |

|-----------------|---------------------------------|-------------|-------------|-------------|

| Denk            | BG Address                      | BG0~BG2     | BG0~BG2     | BG0~BG1     |

| Bank<br>Address | Bank Address in a BG            | BA0~BA1     | BA0~BA1     | BA0~BA1     |

| Address         | # BG / # Banks per BG / # Banks | 8/4/32      | 8 / 4 / 32  | 4 / 4 / 16  |

| ,               | Row Address                     | R0~R17      | R0~R17      | R0~R17      |

|                 | Column Address                  | C0~C10      | C0~C9       | C0~C9       |

|                 | Page size                       | 1KB         | 1KB         | 2KB         |

| Chip            | IDs / Maximum Stack Height      | CID0~2 / 8H | CID0~2 / 8H | CID0~2 / 8H |

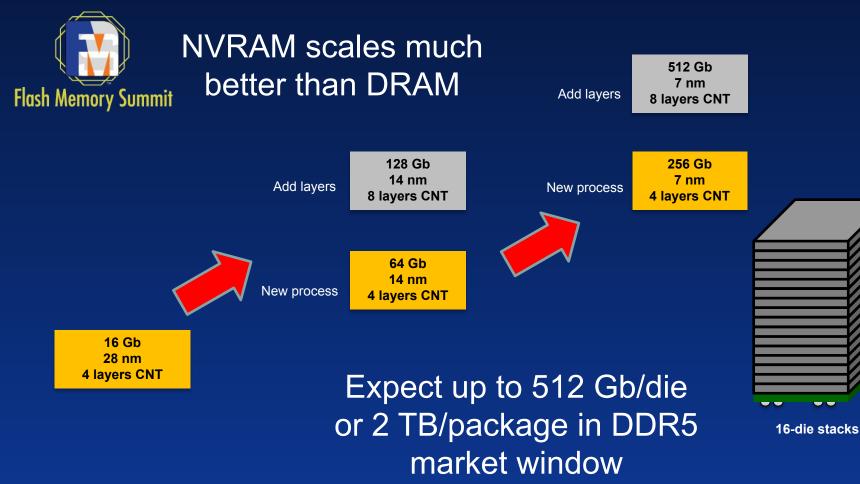

This specific excerpt highlights the upper limit of the DDR5 protocol

16H 3DS stack of 32 Gb die = 512 Gb per pkg

8H 3DS stack of 64 Gb die = 512 Gb per pkg

Santa Clara, CA August 2019

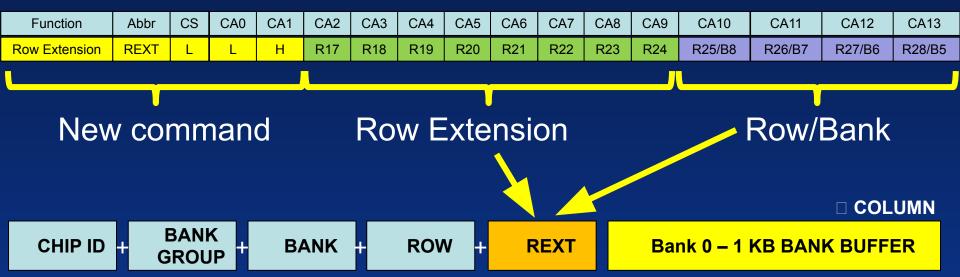

CHIP ID 3 "STOLEN" TO MAKE R17

| Function | Abbrevia-<br>tion | . C 9 n | CA Pins |     |     |     |     |       |     |     |     |     |      |                 |      |                |

|----------|-------------------|---------|---------|-----|-----|-----|-----|-------|-----|-----|-----|-----|------|-----------------|------|----------------|

| Function |                   | CS_n    | CA0     | CA1 | CA2 | CA3 | CA4 | CA5   | CA6 | CA7 | CA8 | CA9 | CA10 | CA11            | CA12 | CA13           |

| Activate | ACT               | L       | L       | L   | R0  | R1  | R2  | R3    | BA0 | BA1 | BG0 | BG1 | BG2  | CID0            | CID1 | CID2/<br>DDPID |

|          |                   | Н       | R4      | R5  | R6  | R7  | R8  | R9    | R10 | R11 | R12 | R13 | R14  | R15             | R16  | CID3/<br>R17   |

| Write    | WR                | L       | н       | L   | н   | Н   | L   | BL*=L | BA0 | BA1 | BG0 | BG1 | BG2  | CIDO            | 9.01 | CID2/<br>DDPID |

| Wine     | VVI V             | Н       | V       | C3  | C4  | C5  | C6  | C7    | C8  | C9  | C10 | V   | AP=L | WR<br>Part al=L | V    | CID3           |

| Read     | RD                | L       | н       | L   | н   | н   | Ĥ   | BL*=L | BA0 | BA1 | BG0 | BG1 | BG2  | CID0            | CID1 | CID2/<br>DDPID |

|          |                   | Н       | C2      | C3  | C4  | C5  | C6  | C7    | C8  | C9  | C10 | V   | RP=L | V               | V    | CID3           |

All bit positions are consumed CID3 must be used as R17 for 64 Gb die

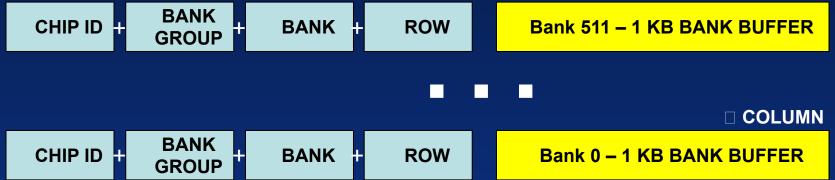

Per DRAM package...

Up to 16 DRAM die...

32 bank buffers...

1 KB per bank buffer...

512 KB max addressable at a time

From controller perspective, each 1 KB block is associated with a specific combination of CID+BG+BA (9 bits) + ROW

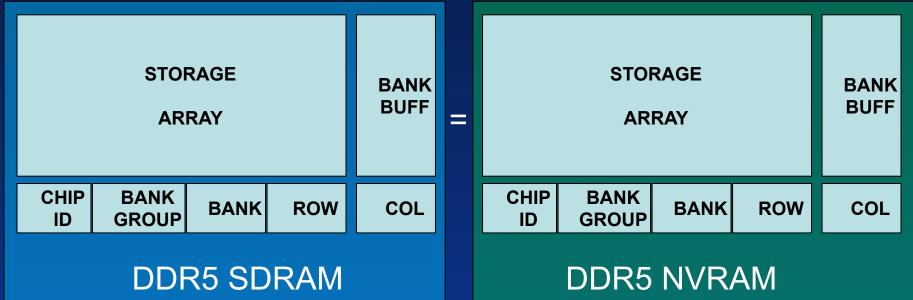

Any storage array may be abstracted

## Nantero NRAM<sup>™</sup>

#### Oh, for example...

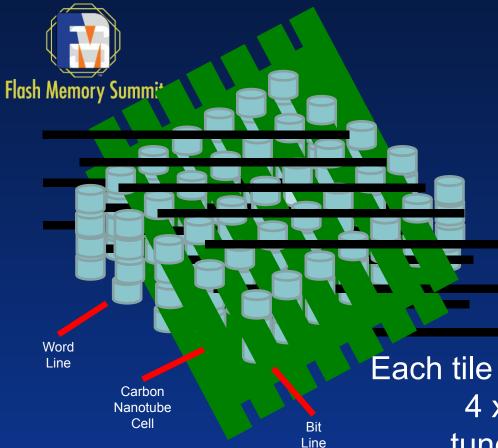

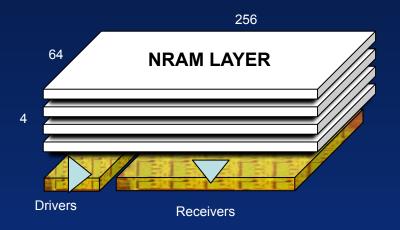

Each tile is a self-contained crosspoint 4 x 64 x 256 = 64 Kb unit tuned to match DDR timing

| Bank<br>Group | 64 Gb = 1024K Tiles = 32K Tiles per Bank |   |   |   |   |   |            |  |  |  |  |

|---------------|------------------------------------------|---|---|---|---|---|------------|--|--|--|--|

| 7             | 6                                        | 5 | 4 | 3 | 2 | 1 | Group<br>0 |  |  |  |  |

| BANK 3        |                                          | 3 | 3 | 3 | 3 | 3 | BANK 3     |  |  |  |  |

| BANK 2        | 2                                        | 2 | 2 | 2 | 2 | 2 | BANK 2     |  |  |  |  |

| BANK 1        | 1                                        | 1 | 1 | 1 | 1 | 1 | BANK 1     |  |  |  |  |

| BANK 0        | 0                                        | 0 | 0 | 0 | 0 | 0 | BANK 0     |  |  |  |  |

#### **DDR5 SDRAM**

| ACTIVATE R/W R/W R/W R/W PRECHARGE ACTIVATE R/W R/W PRECHARGE REFRESH |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

SDRAM must close banks before reactivating

SDRAM must close banks prior to refreshing

Memory controller must buffer I/O data during refresh cycles

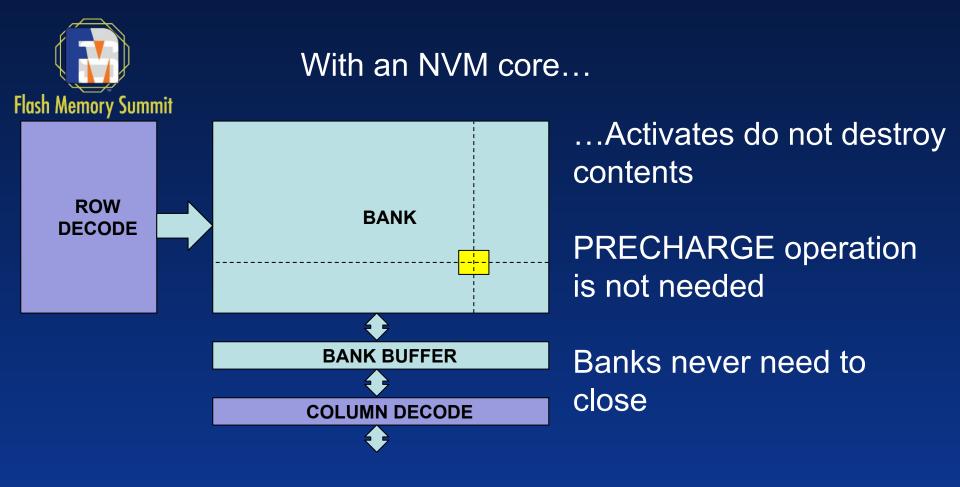

#### **DDR5 NVRAM**

| ACTIVATE | R/W | R/W | R/W | R/W | ACTIVATE | R/W |

|----------|-----|-----|-----|-----|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|          |     |     |     |     |          |     |     |     |     |     |     |     |     |     |     |

NVRAM is always available for data transfer 15% or more throughput at the same clock frequency

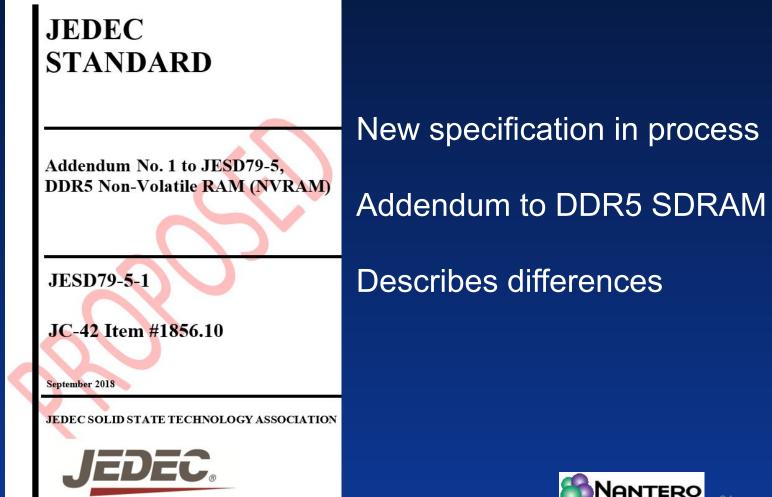

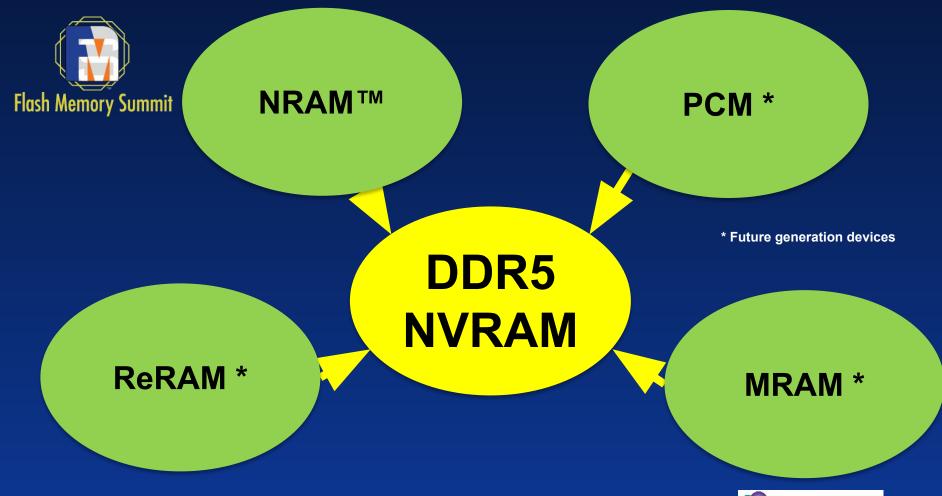

Other persistent memory device types are emerging They are also covered by the DDR5 NVRAM specification Some possible differences from NRAM:

- Timing variations (activation, write recovery, etc.)

- Different page size per bank

- Destructive ACTIVATE (PRECHARGE needed)

- Persistence defined from FLUSH command

#### Common DDR5 NVRAM Feature Set

# Differences captured in the SPD

#### **DDR5 NVRAM Core Functions**

Activate Read Write Precharge Refresh Self Refresh

Fetches data from the array to sense amps Read data from sense amps Write data to sense amps NOP NOP NOP

# Closer to the dream of a LOAD/STORE memory

Compatible but more efficient

# Won't the DDR5 limit of 32Gb per die limit NVRAM?

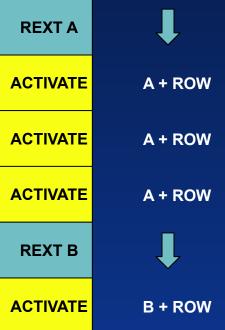

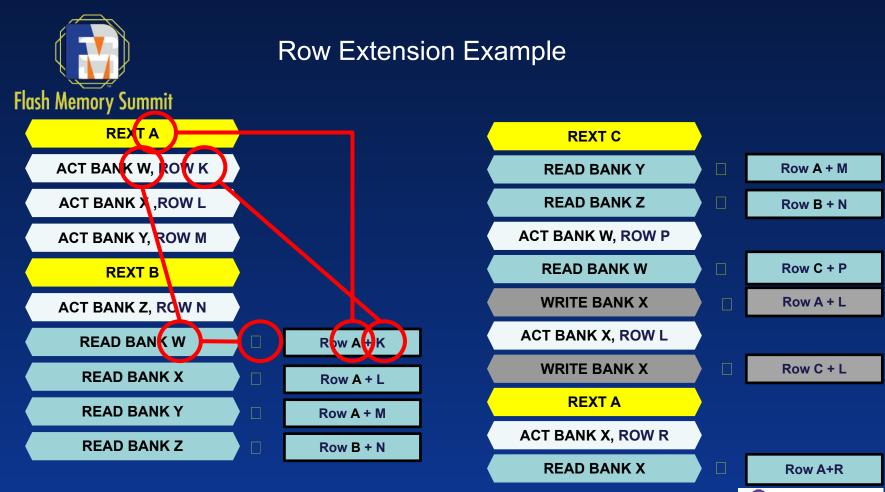

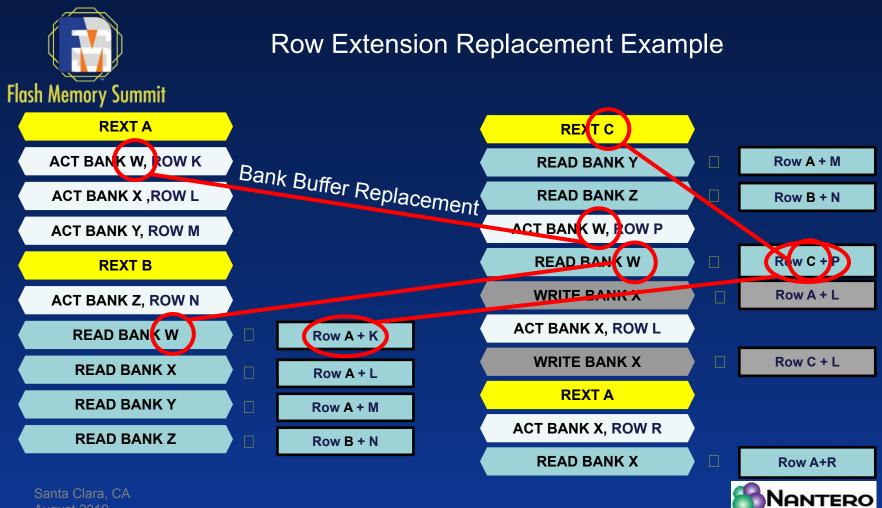

Introducing Row Extension Based on the 1980s "Expanded Memory" concept Adds a sort of paging register Improved semantics for efficiency by only impacting ACTIVATE

#### Impact: Extends # address bits associated with bank buffer

NANTERO

~

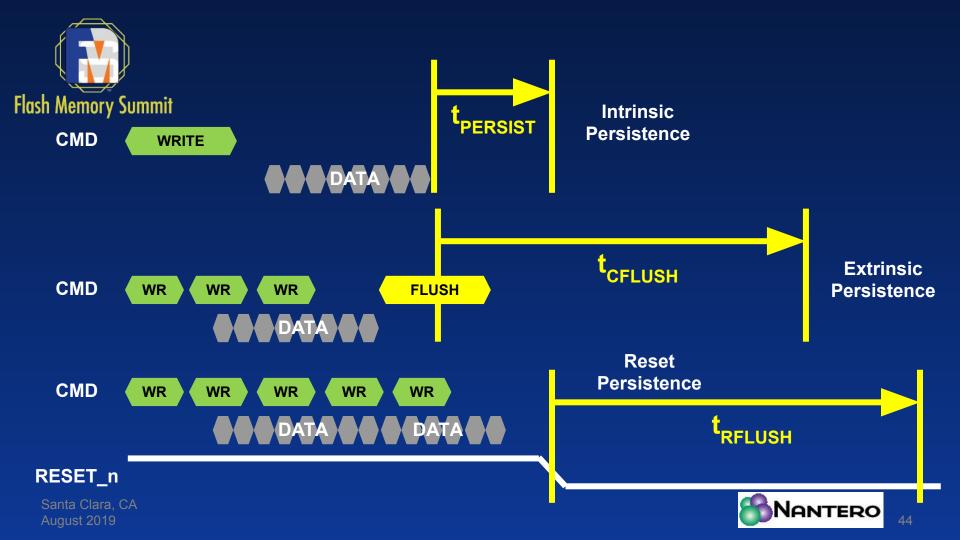

#### "Power fail isn't the only concern" "Need to know exactly when data is committed to NVM cells"

New persistence definitions address this

# Provides a safe place for competitors to jointly develop specifications

Wider, more rapid acceptance

Documents features for controller designers

### **Questions?**

## Bill Gervasi Principal Systems Architect bilge@Nantero.com