### The Engine

### SRAM & DRAM Endurance and Speed with STT MRAM

Les Crudele / Andrew J. Walker PhD

- The Leaking Creaking Pyramid

- STT-MRAM: A Compelling SRAM Replacement

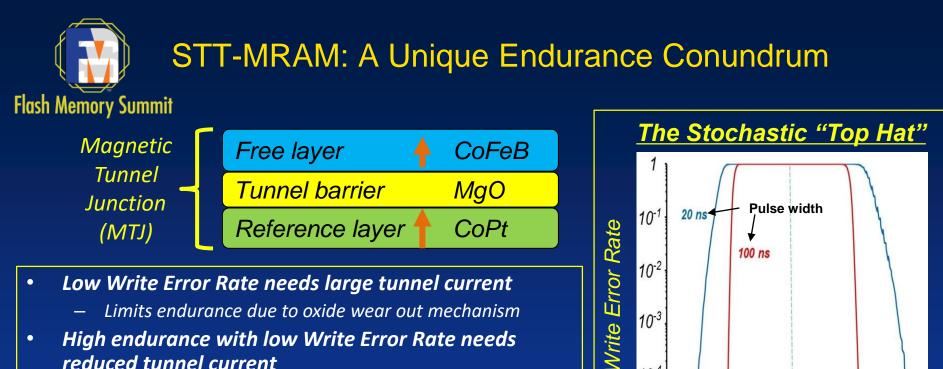

- STT-MRAM: A Unique Endurance Conundrum

- The ENGINE for SRAM & DRAM Endurance and Speed

- The Physics of the ENGINE

- ENGINE Emulation

- Data from Emulated ENGINE

- ENGINE Benefits Takes MRAM Mainstream !

- The Performance, Energy and Cost Advantage

- Conclusions

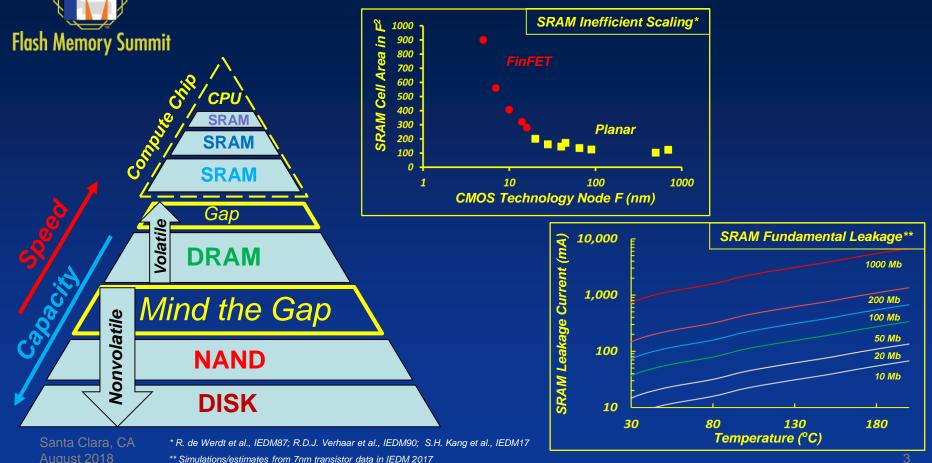

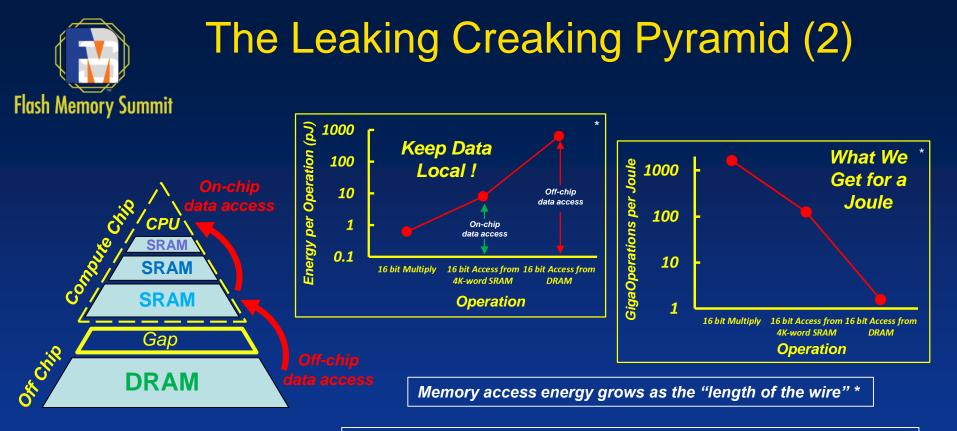

# The Leaking Creaking Pyramid (1)

> 60% of system energy used is in data movements to and from DRAM \*\*

\* A. Pedram et al., "Dark Memory and Accelerator-Rich System Optimization in the Dark Silicon Era", IEEE Design & Test, vol.34, April 2017

Santa Clara, CA August 2018

\*\* A. Boroumand et al., "Google Workloads for Consumer Devices: Mitigating Data Movement Bottlenecks", ASPLOS'18, March 2018

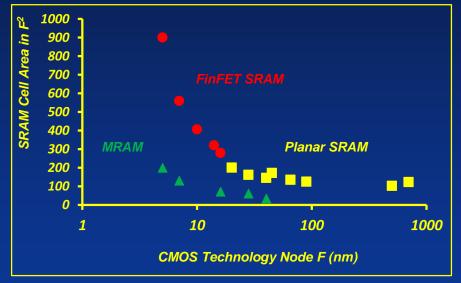

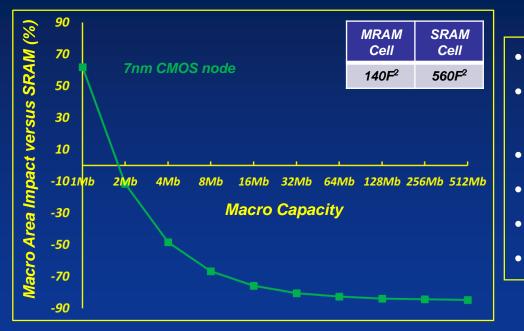

- ✓ <u>Size</u> : Dramatic bitcell reduction

- ✓ Leakage : No array leakage

- Persistence : Data retained

- ✓ <u>On-chip</u> : Reduces DRAM accesses

- ✓ <u>Rad-Hard</u>

- ✓ <u>But:</u>

- Limiting Endurance Conundrum

- Non-symmetric R/W

- Disturbs with fast read

reduced tunnel current

- Make Free Layer magnetically less "stiff"

- Reduce MTJ area \_

- Use special design techniques The ENGINE

$10^{-4}$

$10^{-5}$ -0.8

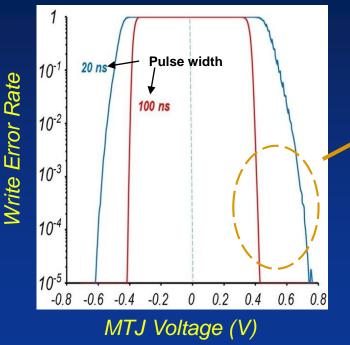

### The Physics of the ENGINE

ite Error

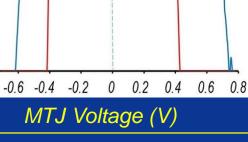

### The Stochastic "Top Hat"

Faster pulse antanta Rate) Increased WER og(W Reduced electrical stress

#### MTJ Voltage (V)

Proprietary Circuit Design allows reduced electrical stress Results in large endurance increase (~ 6 orders of magnitude) Circuit Deals with resultant Write Error Rate increase

- Managed transparently to the user

- No change in latency

- Allows for faster pulses at high endurance

## **ENGINE Emulation**

**Emulation Board** (FPGA emulation of Engine)

**Front Panel** (Control timing, address, patterns, W/R ops etc.)

**Daughter Board** (Contains SPIN's own 4Mb

STT-MRAMs)

Logic Analyzer (Verify addresses, timing, patterns, W/R etc.)

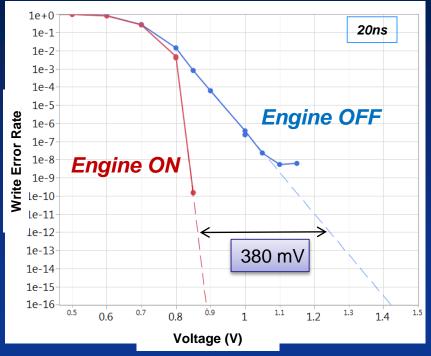

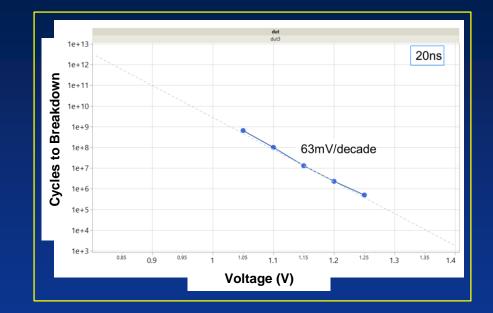

### Data from Emulated ENGINE

~ 6 orders of magnitude endurance boost

- SRAM/DRAM-like Endurance

- ~ 6 orders of magnitude improvement with circuitry alone

- Symmetric R/W

- 10ns capable

- Random R/W

- Looks and feels like an SRAM

- Corrects Read Disturbs allowing Fast Reads

- No user visible errors

### The Performance, Energy and Cost Advantage

- Dramatic area impact

- Maximize large on-chip cache and memory capacity

- Allows persistence on-chip

- Reduces DRAM accesses

- ~ Zero array leakage

- Symmetric Read/Write

### Conclusions

- The ENGINE takes MRAM into the mainstream

- Provides a path for MRAM as SRAM/DRAM replacement

- Uses evolving ecosystem for embedded NV MRAM as a foundation

- Combines low Write Error Rates with SRAM/DRAM-like

endurance resulting in zero user-visible errors

- Achieves fast and symmetric read and write

- Makes MRAM the most likely candidate for SRAM replacement and, eventually, DRAM