## Non-Volatile Memory Modules (NVDIMMs)

Bill Gervasi Principal Systems Architect bilge@Nantero.com

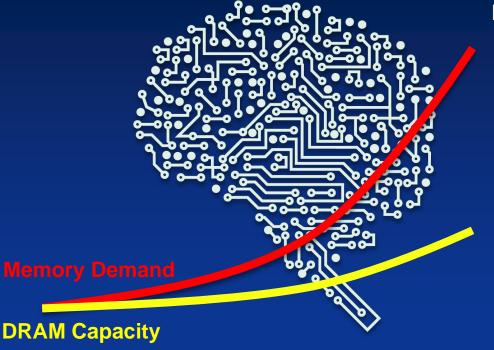

## **Demand Outpacing Capacity**

**In-Memory Computing**

**Artificial Intelligence**

**Machine Learning**

**Deep Learning**

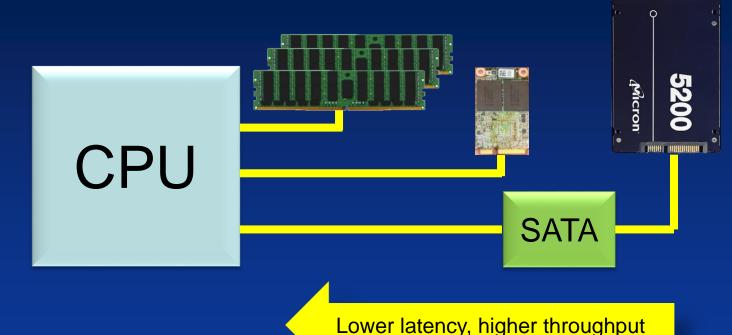

# Chumming Up to the CPU

Santa Clara, CA August 2018

#### Mass storage moving closer to the CPU

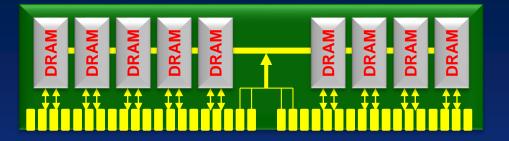

# **DRAM Channel Protocol**

Designed around direct connection to a DDR device Fully deterministic operation required Multiplexed address bus with:

- Chip selects (ranks)

- Rows

- Columns

- Commands

**DDR4 limits:**

- 16 Gb per chip

- 144 chips per module

- 256 GB per DIMM

#### **DDR5** limits

- 32 Gb per chip

- 288 chips per module

- 1 TB per DIMM

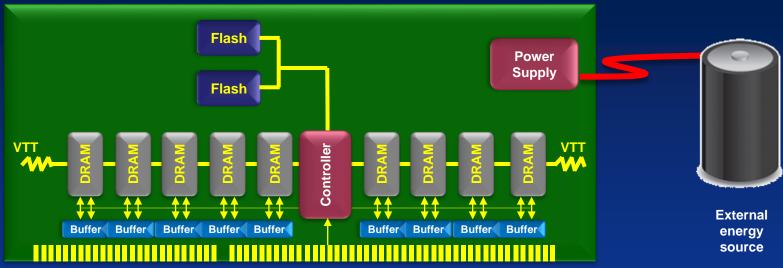

# NVDIMM-N, The Simplest Hybrid

CPU communicates with DRAM only On power fail, Controller copies contents to Flash External energy source powers NVDIMM until backed up

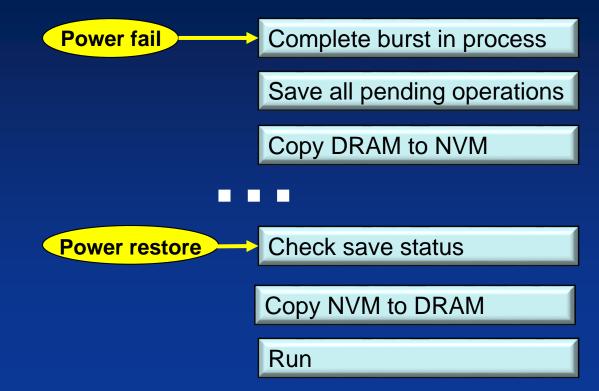

# **NVDIMM-N Backup Protocol**

Storage

PN

CRU

## Why is Persistence Important?

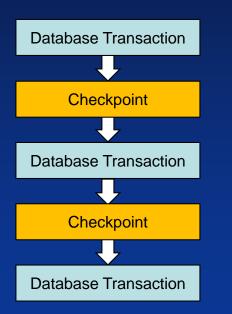

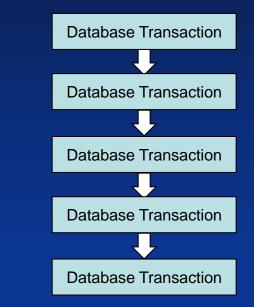

Power failure is a key factor in server software design

> Checkpointing intermediate results to storage affects performance

> > Data persistence near the CPU is a huge improvement in systems architecture

### **Persistence in Main Memory**

### **Old Process**

#### Add Persistence Memory

Transaction critical data

Temporary data

Application code

etc

Persistent Memory

(NVDIMM)

Main

Memory

(DRAM)

#### **New Process**

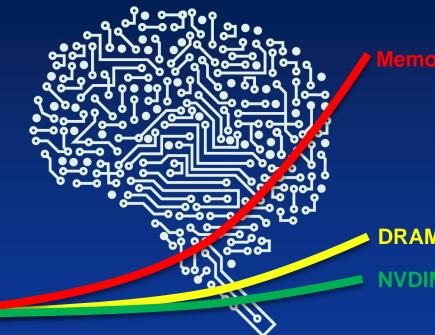

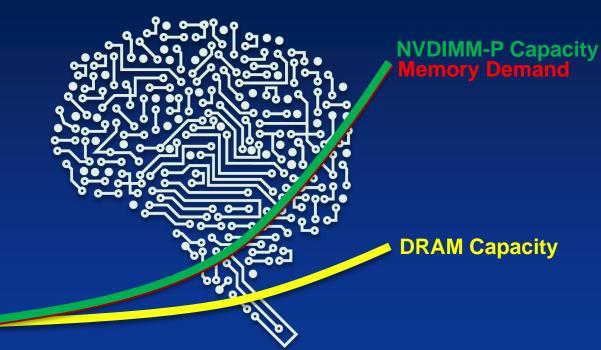

# **NVDIMM-N Capacity Limitations**

Unfortunately, NVDIMM-N doesn't solve the capacity demand... in fact makes it worse

NVDIMM-N capacity is half of the equivalent DRAM module capacity

Does add data persistence

Memory Demand

DRAM Capacity

**NVDIMM-N** Capacity

## **Universe of Persistent Memories**

Many technologies coming online to fill the gap between DRAM and Flash

Wasteland

Hard Disk

SSD

**NVMe**

DDR DRAM Painfully slow Lotsa cheap bits Low endurance

Flash

Moderate speed Moderate endurance Capacity range

> Phase Change 3D Xpoint Resistive RAM Magnetic RAM

> > PMs do not replace DRAM though

Santa Clara, CA August 2018

10

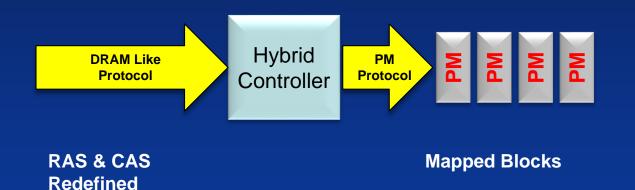

# Virtualizing the DRAM Channel

Incorporating PM into the DRAM channel requires:

- Mapping devices into the DRAM address range

- Allowing for non-determinism for bookkeeping operations

Limited write endurance forces PMs to go offline for operations such as wear leveling

Media agnostic; any PM can be on the local bus

## Virtualizing the DRAM Channel

#### DDR4

| Function_                                                          | tio          | C                              |    | CS_n | ACT | RAS        | CAS        | WE_       | BG0-            | BA0-     | C2- | A12/             | A17,        | A10/     | A0- |

|--------------------------------------------------------------------|--------------|--------------------------------|----|------|-----|------------|------------|-----------|-----------------|----------|-----|------------------|-------------|----------|-----|

|                                                                    | via.         | Previous Currer<br>Cycle Cycle |    |      | _n  | _n/<br>Ā16 | _n/<br>Ā15 | n/<br>A14 | BG1             | BA1      | C0  | BC_n             | A13,<br>A11 | AP.      | A9  |

|                                                                    | Abbreviation | -,                             | -, |      |     | AIU        | AIJ        | AIA       |                 |          |     |                  | AIL         |          |     |

| Mode Register Set                                                  | MRS          |                                |    |      |     |            |            |           | BG              | BA       | V   |                  |             |          |     |

| <b>.</b>                                                           |              | H.                             | H, | L,   | н   | L,         | Ļ          | L,        | BG.<br>V        |          | V   |                  | OP C        |          |     |

| Refresh                                                            | REF.         | H.                             | H, | L,   | н   | L,         | Ļ          | H,        | - N.            | V.       |     | V.               | V.          | V.       | V   |

| Self Refresh Entry                                                 | SRE          | H.                             | Ļ  | Ļ    | H   | Ļ          | Ļ          | H.        | V.              | V.       | V   | V.               | V.          | V.       | V   |

| Self Refresh Exit                                                  | SRX          | L,                             | H  | H.   | X   | X          | X          | X         | X<br>V          | X        | X   | X                | X           | X        | X   |

| Single Bank Precharge                                              | PRE          | н                              | н  | Ļ    | H   | H,         | H<br>H     | H,        | V.<br>BG        | V.<br>BA | V   | V.<br>V          | V.<br>V     | V,       | V   |

| · · ·                                                              | PRE          | л<br>Н                         | П  | Ц.   | н   | L,         | H          | L,        | V               |          | V   | V.               | V.<br>V     | <u>ц</u> | V   |

| Precharge all Banks<br>RFU                                         | REU          | H<br>H                         | H  | Ļ    | H   | Ļ          | H<br>H     | L.<br>H   | V.              | V.       | V   | RFU              | V.          | H,       | V   |

|                                                                    | ACT          | H                              | Н  | L    | н   | L          | Row        |           | BG              |          |     |                  |             |          |     |

| Bank Activate                                                      | ACT.         | Π,                             | ц  | Ļ    | L   | Ade        | ress(      | RA)       | BG              | ΒĄ       | v   | Row Address (RA) |             |          |     |

| Write (Fixed BL8 or BC4)                                           | WR.          | H,                             | H, | Ļ    | н   | H,         | Ļ          | Ļ         | BG              | BĄ       | V   | V.               | V.          | Ļ        | CĄ  |

| Write (BC4, on the Fly)                                            | WRS4         | H,                             | H, | Ļ    | н   | H,         | Ļ          | Ļ         | BG              | ΒĄ       | V   | Ľ,               | V.          | Ļ        | CĄ  |

| Write (BL8, on the Fly)                                            | WRS8         | Н,                             | H, | L,   | Н   | H,         | Ļ          | Ļ         | BG              | ΒĄ       | V   | H,               | V.          | Ц.       | CĄ  |

| Write with Auto Precharge                                          | WRĄ          | H,                             | H, | Ļ    | н   | H,         | Ļ          | Ļ         | BG              | BĄ       | V   | V.               | V.          | H,       | CĄ  |

| (Fixed BL8 or BC4)                                                 |              |                                |    |      |     |            |            |           |                 |          |     |                  |             |          |     |

| Write with Auto Precharge<br>(BC4, on the Fly)                     | WRAS4        | Η.                             | H, | Ļ    | н   | H.         | Ļ          | Ļ         | BG              | ΒĄ       | V   | L.               | V.          | H,       | CĄ  |

| Write with Auto Precharge<br>(BL8, on the Fly)                     | WRAS8        | H.                             | H. | Ļ    | н   | H,         | Ļ          | Ļ         | BG              | ΒĄ       | V   | H,               | V.          | H.       | CĄ  |

| Read (Fixed BL8 or BC4)                                            | RD.          | н                              | H  | L    | н   | H          | L          | H         | BG              | BĄ       | V   | V.               | V.          | L        | CA  |

| Read (BC4, on the Fly)                                             | RDS4         | H                              | H  | Ļ    | н   | H          | Ļ          | H         | BG              | BĄ       | V   | Ļ                | V           | Ļ        | CA  |

| Read (BL8, on the Fly)                                             | RDS8         | H.                             | H, | Ļ    | н   | H,         | Ļ          | H.        | BG              | BĄ       | V   | H                | V.          | Ļ        | CĄ  |

| Read with Auto Precharge<br>(Fixed BL8 or BC4)                     | RDĄ          | H.                             | H, | Ļ    | н   | H.         | Ļ          | H.        | BG              | ΒĄ       | V   | V.               | V.          | H,       | CĄ  |

| Read with Auto Precharge<br>(BC4, on the Fly)                      | RDAS4        | Ą                              | H, | Ļ    | н   | H.         | Ļ          | H.        | BG <sub>.</sub> | ΒĄ       | V   | Ļ                | V.          | H,       | CĄ  |

| (BC4, on the Fly)<br>Read with Auto Precharge<br>(BL8, on the Fly) | RDAS8        | ų                              | H, | Ļ    | н   | H          | Ļ          | H         | BĢ              | ΒĄ       | V   | H.               | V.          | H,       | CĄ  |

| No Operation                                                       | NOP.         | H                              | H  | Ļ    | н   | H          | H          | H         | V               | V.       | V   | V.               | V           | V.       | V.  |

| Device Deselected                                                  | DES          | H                              | H, | H    | Х   | X          | X          | X         | X               | X        | Х   | X                | X           | X        | X   |

| Power Down Entry                                                   | PDE          | H                              | Ļ  | H,   | Х   | X          | X          | X         | X               | X        | X   | X                | X           | X        | X   |

| Power Down Exit                                                    | PDX          | Ļ                              | H, | H,   | Х   | X          | X          | X         | X               | X        | X   | X                | X           | X        | X   |

| ZQ calibration Long                                                | ZQCL         | H                              | H  | Ļ    | н   | H          | H          | Ļ         | V               | V        | V   | V                | V           | H        | V   |

| ZQ calibration Short                                               | ZQCS         | H                              | H  | L    | н   | H          | H          | L         | V.              | V.       | V   | V.               | V.          | Ļ        | V.  |

#### **NVDIMM-P**

| Function<br>(Reference)    | Previous CKE_0 | Current | $cs_n$ | ACT_n       | RAS_n/A16 | CAS_n / A15 | WE_n / A14 | BG1-BG0     | BA1-BA0 | C2-C0     | A12 / BC_n | A17                | A13                   | A11                            | A10 / AP              | A9-A0                         |                                          |

|----------------------------|----------------|---------|--------|-------------|-----------|-------------|------------|-------------|---------|-----------|------------|--------------------|-----------------------|--------------------------------|-----------------------|-------------------------------|------------------------------------------|

| MRS<br>(Mode Register Set) | н              | н       | L      | Н           | L         | L           | L          | v           | v       | v         |            | OP CODE            |                       |                                |                       |                               |                                          |

| XADR                       | н              | н       | L      | ADDR[22:12] |           |             |            |             |         |           |            | REAI<br>PWRI<br>XV | [4:<br>TE : V<br>WRIT | ADDR[11:2]                     |                       |                               |                                          |

| XWRITE                     | Н              | Н       | L      | Н           | Н         | L           | L          | ADDR[39:33] |         |           | RFU        |                    |                       | L                              | RFU                   | ADDR[32:23]                   |                                          |

| PWRITE                     | Н              | Н       | L      | Н           | Н         | L           | L          | ADDR[39:33] |         | WGID[7:5] |            | Н                  | Persist               | ADDR[32:23]                    |                       |                               |                                          |

| SEND                       | Н              | Н       | L      | Н           | Н         | L           | Н          | RFU         |         | RFU       |            | L                  | L                     | RFU                            |                       |                               |                                          |

| SEND-W PER                 | Н              | Н       | L      | Н           | Н         | L           | Н          | RFU         |         |           | RFU        |                    | L                     | Н                              | RFU                   |                               |                                          |

| SREAD                      | Н              | Н       | L      | Н           | Н         | L           | Н          | ADDR[39:33] |         | RID[7:5]  |            | Н                  | RFU                   | ADDR[32:23]                    |                       |                               |                                          |

| XREAD                      | Н              | Н       | L      | Н           | L         | Н           | Н          | ADDR[39:33] |         | RID[7:5]  |            | L                  | RFU                   | ADDR[32:23]                    |                       |                               |                                          |

| UNMAP                      | н              | н       | L      | Н           | L         | Н           | Н          | ADI         | DR[39   | [39:33] L |            | L                  | L                     | Н                              | OPCO<br>DE[0]         | ADDR[32:23]                   |                                          |

| FLUSH                      | н              | н       | L      | Н           | L         | Н           | Н          | RFU         |         | Н         | н          | L                  | Н                     | <del>RFU</del><br><u>Final</u> | FL[1:0]+<br>WGID[7:0] |                               |                                          |

| ЮР                         | н              | н       | L      | Н           | L         | Н           | Н          | RFU         |         | RFU       |            | L                  | Н                     | Н                              | Н                     | RFU                           | RFU[2:0]+<br>IOP TS[1:0]+<br>IOP TU[4:0] |

| NOP                        | Н              | Н       | L      | Н           | Н         | Н           | Н          | V           |         | V         | V          | v                  | V                     | V                              | V                     |                               |                                          |

| DESELECT                   | Н              | Н       | Н      | Х           | Х         | Х           | Х          | Х           |         | Х         | Х          | Х                  | Х                     | Х                              | X                     |                               |                                          |

| POWER DOWN<br>ENTRY        | н              | L       | Н      | х           | х         | х           | х          |             | х       |           | х          | x                  | х                     | х                              | Х                     | X IOP TS[1:0]+<br>IOP TU[4:0] |                                          |

| POWER DOWN<br>EXIT         | L              | н       | Н      | х           | х         | х           | х          |             | х       |           | х          | х                  | х                     | х                              | Х                     | х                             |                                          |

| ZQ Calibration Long        | Н              | Н       | L      | Н           | Н         | Н           | L          |             | V       |           | V          | V                  | V                     | v                              | Н                     | V                             |                                          |

| ZQ Calibration Short       | Н              | Н       | L      | Н           | Н         | Н           | L          |             | V       |           | V          | V                  | V                     | V                              | L                     | V                             |                                          |

Santa Clara, CA August 2018

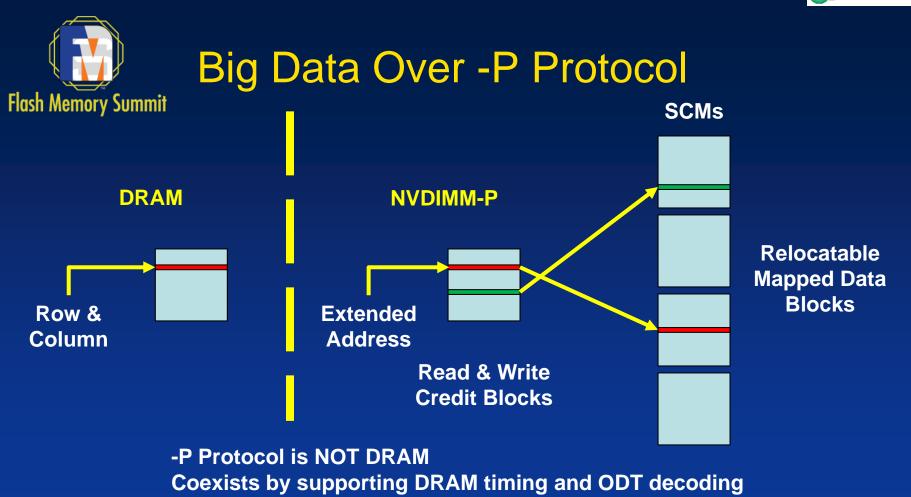

#### Different protocols but can share the same wires

### Non-deterministic credit based system allows time for bookkeeping

Out-of-order data returned with ID

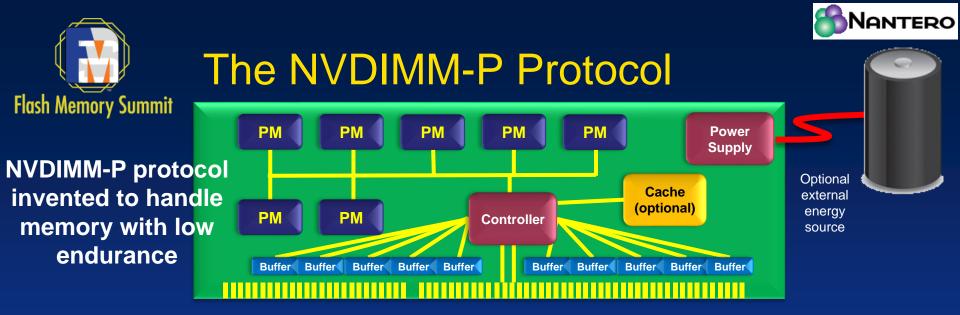

## **NVDIMM-P** Capacity

NVDIMM-P Protocol extends the DDR interface to enable big data

Out-of-order nondeterministic data allows for bookkeeping such as wear leveling

**Requires new CPU**

#### DDR5 NVDIMM-P too

### Software Issues

#### All NVDIMM-N

No problem, all memory persistent, all memory has same performance No problem, all memory persistent, all memory has same performance

All NVDIMM-P

Symmetric solutions are simplest; no software changes, accept the performance you get

Mix of NVDIMM-N & DRAM

Complicates the solution Software must separate persistent data from ephemeral data

Mix of NVDIMM-P & DRAM

NVDIMM-P can mount as extended memory with asymmetric performance or simply as SSD

Asymmetric solutions are more complicated, software partitioning required, many solution punt by mounting NVDIMM as an SSD

## Advantage of Large Capacity PM

### Persistent Main Memory

Main Memory (e.g., DRAM) Much larger data sets align with increase in in-memory analysis memory requirements

Al, data mining, etc

Far fewer flushes to external mass storage

Power fail safe

Mass Storage (SSD, etc)

# **Tuning Software for Persistence**

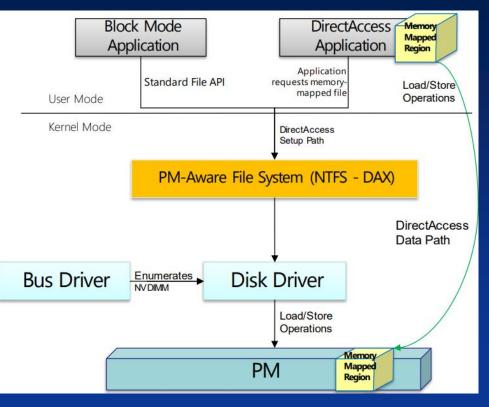

Operating systems have "new" hooks for persistent memory

Both disk mount and direct access enabled

## **Data Security**

Persistent memory has generated concerns about data security

Some systems prefer to encrypt in the CPU

NVDIMMs specifications adding on-DIMM encryption option

May be required for systems with DMA to the DRAM channel

Memory capacity demands exceeding DRAM roadmap DRAM protocol limited to 16 Gb for DDR4, 32 Gb for DDR5 **NVDIMM-N** adds data persistence **NVDIMM-P** allows media independent expansion Software must deal with performance/feature asymmetry Data encryption coming

# Bill Gervasi Principal Systems Architect bilge@Nantero.com